Inside Intel Tech Tour 2025: Panther Lake And Clearwater Forest Built On 18A

Intel Clearwater Forest: Up To 288 Cores With 5X The L3 Cache

Xeon 6+ series processors based on Clearwater Forest will feature up to 288 Darkmont-based CPU E-cores on a single package, fabricated on Intel's 18A process. The chips will also feature up to 576MB of L3 cache – which is a massive 5X improvement over the previous-gen, and connect to up to twelve channels of DDR5 memory, operating at speeds up to 8000 MT/s. Intel's current gen Sierra Forest Xeons offer up to eight memory channels operating at up to 6400MT/s.

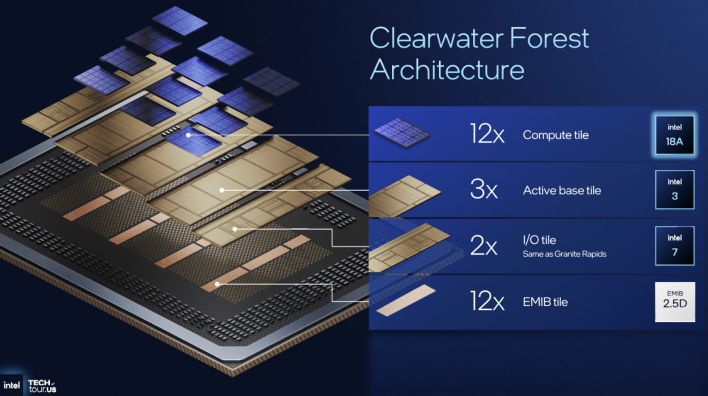

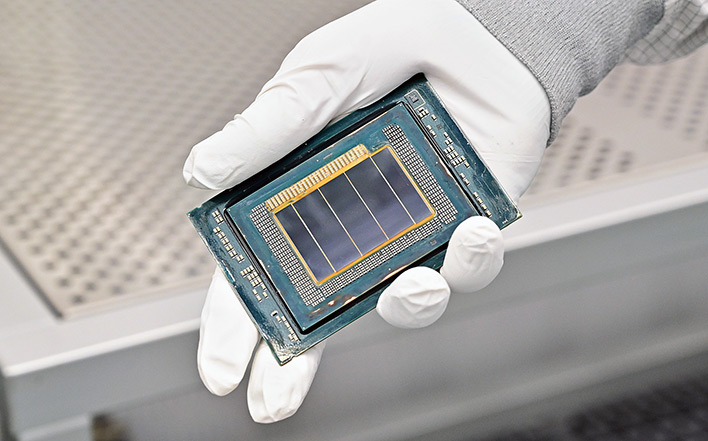

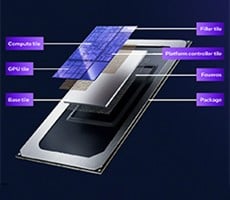

Clearwater Forest is the successor to Sierra Forest and targets Cloud Native operations and 5G telecom infrastructure. The processors are built using twelve CPU or compute tiles, each with eight clusters of four CPU cores. Those cores are based on the same fundamental Darkmont core architecture found in Panther Lake, which is an evolution of the Skymont E-core architecture used in Lunar Lake and Arrow Lake processors.

There's been some discussion about whether Darkmont is simply the name of Skymont built on Intel’s new 18A process, but there are some enhancements to the architecture to improve on the power and clock gating capabilities, and support for Intel Application Energy Telemetry is included, which in-turn should improve efficiency with most workloads. As we’ve mentioned many times in the past, 18A also features a couple of bleeding-edge technologies, like RibbonFET gate all-around transistors and PowerVia with backside power delivery.

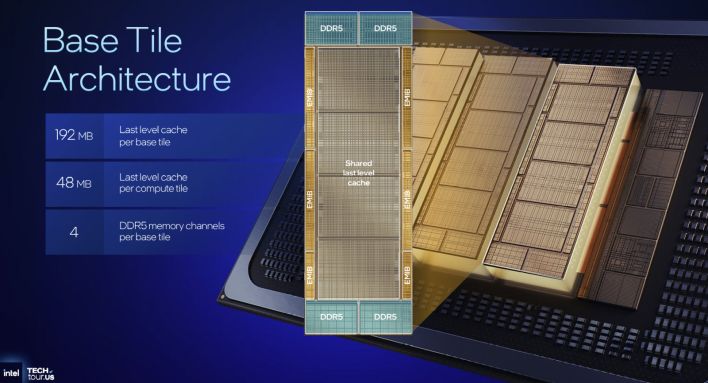

The compute tiles on Clearwater Forest are bonded to three active base tiles using Intel’s Foveros Direct 3D technology. The base tiles are where memory channels and LLC reside; 4 memory channels per tile, with 192MB of LLC, or 48MB per compute tile. The chips are also outfitted with two I/O tiles and 12 EMIB (Embedded Multi-Die Interconnect Bridge) tiles link everything together.

Darkmont features wider, deeper and more accurate branch prediction, with 9-wide decode and 8-wide allocation, a massive 26 execution ports, and three separate instruction decoders, each of which can decode three instructions per cycle for a 50% gain over the previous generation. L2 cache bandwidth has also been doubled to 128B/cycle and the L1 data cache ECC can recover better from errors – Darkmont can correct 1-bit errors and detect 2-bit errors. All told, Intel says that IPC is up by 17% on Clearwater Forest, which when coupled with the platform’s increased memory bandwidth, should boost performance considerably.

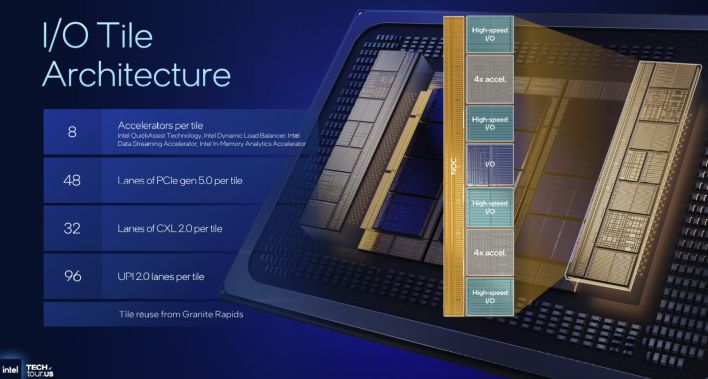

Intel claims that a two-socket (2P) Clearwater Forest system with dual 288-core Xeon 6+ processors, equipped with 8000MT/s memory can achieve up to 1.3 TB/second of realized memory bandwidth, and that the configuration will support up to 3TB of total memory capacity. Each socket gets 96 lanes of PCIe 5.0 connectivity, including 64 lanes of CXL. Altogether, with 576 cores in a 2P system, Intel says the setup can achieve 59 TFLOPS, which is pretty impressive for a CPU.

With all of those cores at play, one of Clearwater Forest’s big advantages is density. As such, Intel is focused on engaging with customers still riding on older Xeon hardware to upgrade, because Clearwater Forest could have a major impact on TCO. Versus 2nd-Gen Intel Xeon chips, for example, customers can potentially slash power by 75 kilowatts and reduce space requirements by about 71%, or achieve an 8:1 sever consolidation. Intel claims the performance-per-watt is also 3.5x better than the older second-generation Xeon parts.

We should also note that Xeon 6+ processors based on Clearwater Forest will be compatible with the previous-generation Xeon 6900 platform. That should accelerate validation and speed up time to market with all of Intel’s server partners.

Intel Tech Tour 2025: Key Takeaways

All told, we think Intel is set up for initial success heading into 2026. Intel 18A was co-developed with Panther Lake and Clearwater Forest, so the process should be well tuned from the outset for the company’s next-gen processors. Engagement with third-party customers may not be what Intel had initially hoped, but we suspect things will change for the better with 18A-P, which is a more performance-optimized iteration of the 18A node, better suited for mobile applications and efficiency-first, power-constrained use cases.Initial impressions are that Panther Lake and Clearwater Forest will be strong products. Everything about Panther Lake is either higher-performing or more efficient than previous-gen architectures and Intel is aggressively targeting a wide range of applications, from robotics to AI PCs, to POS systems to computer vision at the edge. Panther Lake is not just about the next wave of laptops. The NPU is only a mild upgrade if you strictly look at peak TOPS, but it’s significantly smaller and more power efficient. The new Cougar Cove P-cores and Darkmont E-core and LPE-cores, however, should offer a significant performance boost, the new IPU is more capable and efficient, and the Xe3-based iGPUs are improved in a multitude of ways. The platform features all of the latest and greatest IO too.

Clearwater Forest cranks this up quite a few notches as well. In addition to the benefits of manufacturing the compute tiles on a bleeding edge process node, Clearwater Forest features more performance cores, more than 5X the L3 cache, and a massive uplift in memory bandwidth. Xeon 6+ processors based on Clearwater Forest also drop right into existing platform sockets, which have had some time to mature.

We’ll have to wait until we get some hands-on time for our own testing, but at this point we’re optimistic about Panther Lake’s and Clearwater Forest’s prospects. We should have more details to share just after CES in January, so stay tuned to HotHardware.