AMD Zen 2 Architecture Explored: What Makes Ryzen 3000 So Powerful

In this piece, however, we’re going to dig a little deeper and cover the new aspects of AMD's Zen 2 architecture, and what it means for the company's Ryzen 3000 series family of processors. All of the Navi and RDNA-related juicy details as they pertain to the upcoming Radeon RX 5700 series of graphics cards will be made available in separate article. Between all of the articles, we’ll cover the vast majority of products and technologies AMD will be unleashing on the enthusiast community in early July.

As most of you probably know, Zen 2 is the microarchitecture at the foundation of the forthcoming AMD Ryzen 3000 series of processors. Zen 2 is the next evolution of the Zen microarchitecture that debuted with the original Ryzen processors back in 2016. Zen was further refined and optimized for the current family of 2nd Gen Ryzen processors based on Zen+, but Zen 2 is the true, next-gen microarchitecture AMD will be leveraging in its newest line-up of Ryzen CPUs.

AMD has made a number of enhancements with Zen 2 in an effort to improve everything from IPC (instructions per clock) and single-thread performance, to multi-thread scaling, latency, and efficiency/power. The company has made claims that IPC has been improved 15% generation over generation (Zen vs. Zen 2), thanks to better branch prediction, higher integer throughput, and reduced effective latency to memory. These gains are over and above the frequency and power benefits inherent to the processor’s more advanced 7nm manufacturing process.

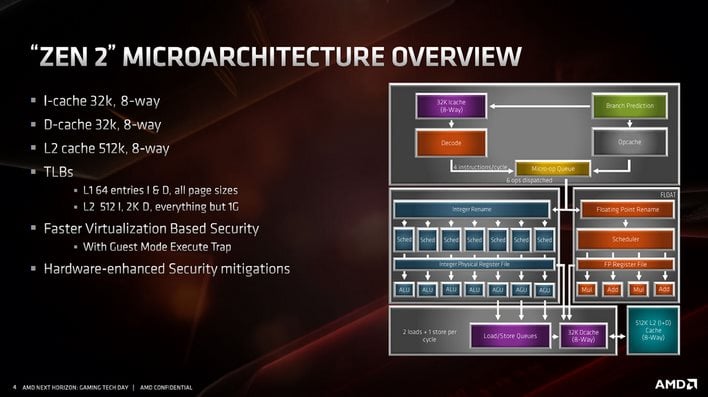

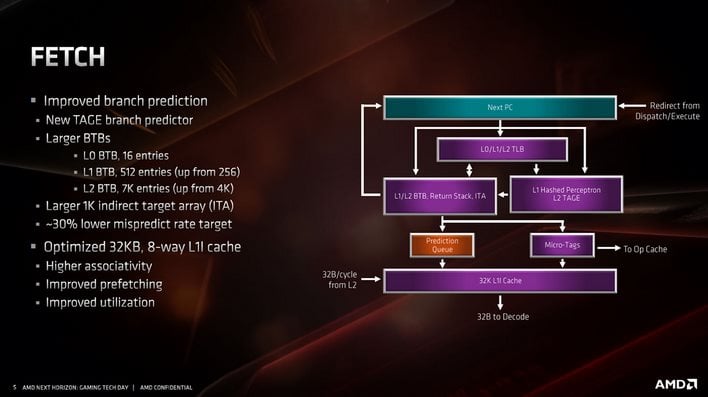

Although Zen 2 builds upon the successes of Zen, many changes have been made to the CPU cores. The updated cores have a new TAGE (Tagged Geometry) Branch Predictor, in addition improved instruction pre-fetching, and a re-optimized L1 cache structure with double the micro-Op cache. The new TAGE branch predictor is able to make selections with better accuracy and granularity and is able to manage longer histories for workloads where that is important. The L1 instruction cache has actually been halved down to 32K, but it is now 8-way associative. The L2 cache remains 512K per core, and is 8-way associative as well. The Zen 2 architecture features more L1 and L2 BTB (Branch Target Buffer) entries and a larger 1K indirect target array as well.

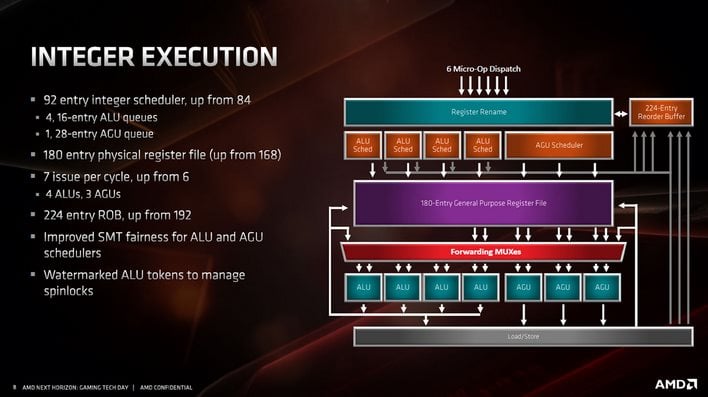

AMD has also increased the Load / Store bandwidth (2 Loads and 1 Store per cycle, 48 entry queue up from 44), Zen 2 has a larger rename space with 180 registers (up from 168), and another Address Generation Unit (AGU) has been added, bringing to total number up to 3 AGUs. Zen 2 can better utilize available CPU resources for increased SMT (Symmetrical Multi-Threading) performance, and it offers a wider, 6 mico-op dispatch as well.

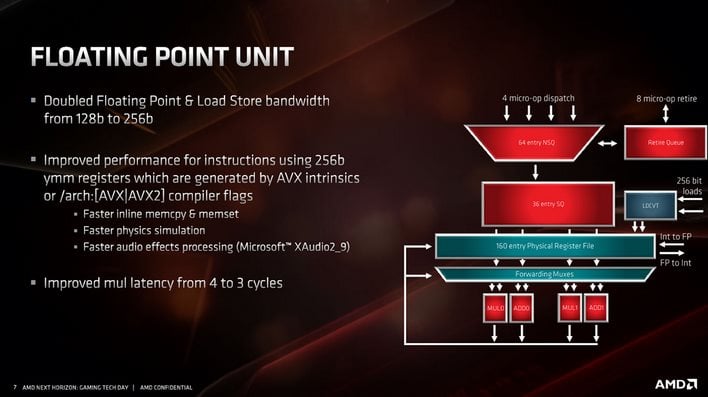

AMD has also significantly beefed up Zen 2’s floating point capabilities. Zen 2 doubles FP performance and Load / Store bandwidth from (128-bit to 256-bit), features 2 x 256-bit Fmacs (built as 4 pipes, 2 Fadd, and 2 Fmul), and offers single-op support for AVX-256 instructions. The architecture has also been optimized to reduced contention in Integer execution.

All of this means, when it comes to serious heavy-lifting in multithreaded and math-intensive workloads, Ryzen 3000 processors will offer significant gains over AMD's previous generation chips, in addition to their previously noted straight-up IPC lift. However, to coin a phrase, but wait there's more...