Inside Snapdragon X2 Elite: Qualcomm’s Next-Gen PC Chip Promises Big Gains

| Qualcomm Snapdragon X2 Elite: MSRP TBD Qualcomm's second generation PC processor, the Snapdragon X2 Elite, improves upon its predecessor in virtually every way, with more cores, increased performance, and enhanced efficiency.

|

|||

|

|

||

Qualcomm announced its second-generation PC processor – the Snapdragon X2 Elite – at its Snapdragon Summit last month, and revealed some early details and performance expectations. Despite entering a new market with the original Snapdragon X Elite and facing significant headwinds from incumbents Intel and AMD, Qualcomm managed to become Microsoft’s exclusive launch partner for Copilot+ PCs with the original Snapdragon X, and also landed quite a few design wins from a number of major notebook OEMs.

The Snapdragon X2 Elite takes everything about its predecessor and cranks it up a few notches, especially in terms of performance and efficiency. Qualcomm claims there have been over 100 architectural and microarchitectural improvements made to the Snapdragon X2 Elite, and that it will offer class-leading efficiency and performance on both single- and multi-threaded workloads. This new chip will also be arriving at a time when far more software is Arm-native, while Microsoft has made significant strides with its Prism emulation engine in the latest versions of Windows 11.

With all of that in mind, the stage seems set for Qualcomm to muscle away some additional market share from the incumbents in the laptop, notebook, and small form factor PC markets—assuming the Snapdragon X2 Elite platform delivers on its promises, of course.

Watch Our Interview With Qualcomm's Lucian Codrescu

Snapdragon X2 Elite High-Level Platform Features

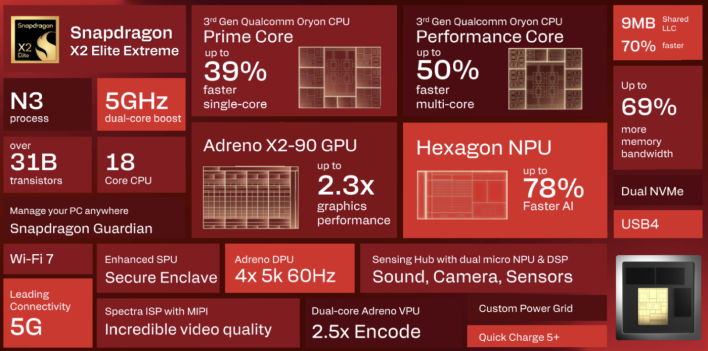

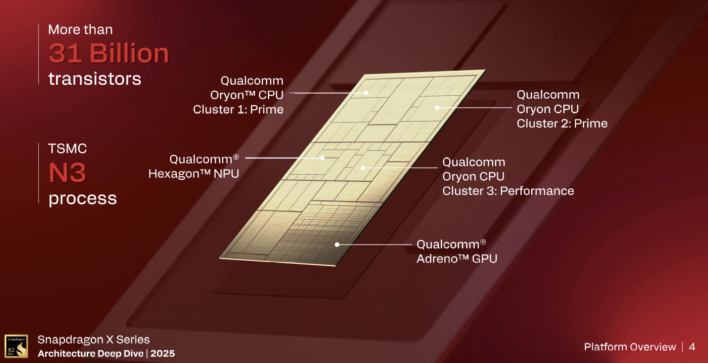

The Snapdragon X2 Elite will initially be offered in three flavors: an 18-core Extreme edition, an 18-core base Snapdragon X2 Elite, and a 12-Core X2 Elite that also has a scaled back GPU. The chip is manufactured on TSMC’s N3 process node, and is composed of approximately 31B transistors. Its die size measures about 13.3mm x 16.5mm (219.5mm²) according to my trusty digital calipers.The Snapdragon X2 Elite will also come with varying memory configurations. The top-end Snapdragon X2 Elite Extreme will always feature up to 128GB of on-package memory with a 192-bit memory interface operating as fast as 9,533MT/s. Qualcomm says that this will be the most performant configuration. The 12 and 18-core standard Snapdragon X2 Elites will feature either on-package memory or discrete memory, including support for LPCAMM, to give partners more flexibility with their system designs.

We’ll dive deeper a little later, but we should also mention that the Snapdragon X2 Elite features an improved cache configuration and faster memory fabric as well. The Last Level Cache (LLC) has 70% higher bandwidth than the previous-gen and it can be dynamically shared across all IP blocks in the chip: CPU, GPU, NPU, sensing hub, etc. It’s not a static allocation of cache to the various components, but rather it is dynamically allocated to each block when needed. There’s a high-bandwidth, coherent fabric linking all of the components on the SoC too, which delivers (according to Qualcomm) improved latency and power efficiency over the previous-gen.

The Snapdragon X2 Elite will also feature higher clocks and a new boost / turbo algorithm that’s similar to what Intel and AMD offer with their mobile processors. On the Snapdragon X2 Elite Extreme, for example, when 1 Prime core is active, it will boost up to 5GHz. When 2 cores are active it’ll boost up to 4.8GHz; 3 cores, 4.47GHz, and when 4,5, or 6 cores are active it’ll boost up to 4.45GHz. The chips feature three clusters of 6 Prime or Performance cores each (for 18 total), and clocks are controlled independently on each cluster based on the workload running at the time. The Prime cores will still clock higher than the performance cores, though.

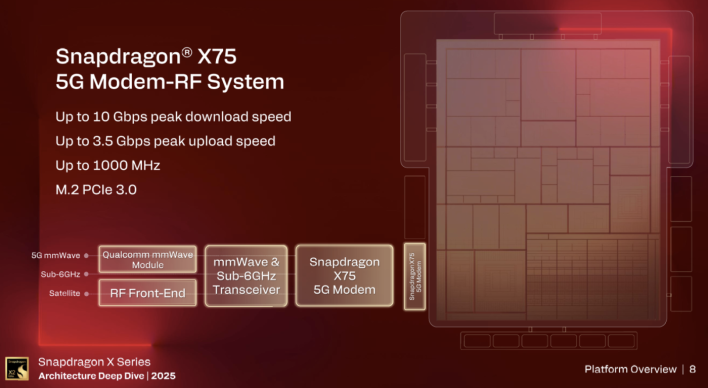

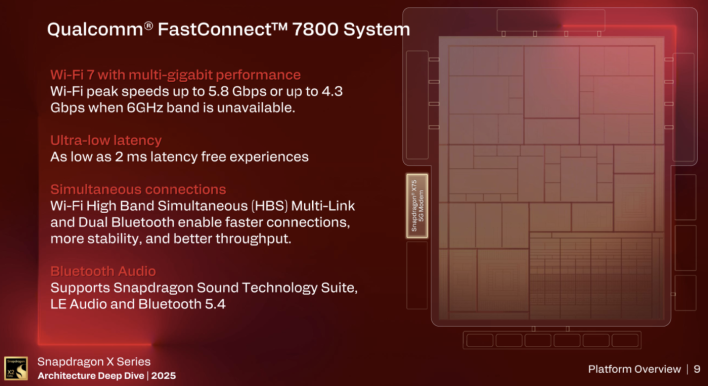

Qualcomm’s Bread And Butter: Wireless Connectivity And IO

Wireless connectivity is also a big part of the Snapdragon X2 Elite. The platform features support for the Snapdragon X75 5G modem-RF system, which offers up to 10GB/s peak download bandwidth and up to 3.5GB/s peak upload. The Snapdragon X75 can utilize up to 1GHz of spectrum and supports sub-6GHz and mmWave connectivity. This fancy modem won’t appear in every Snapdragon X2 Elite system though; it can be integrated into systems via a PCIe 3.0-based M.2 add-in module.

The Qualcomm FastConnect 7800 Wi-Fi system is also part of the Snapdragon X2 Elite platform. FastConnect 7800 supports multi-gig Wi-Fi 7, up to 5.8Gb/s on the 6GHz band and up to 4.2Gb/s on the lower bands. Note that the platform supports always-on connectivity too, which keeps devices connected even when the systems are in suspend states.

Finally, Qualcomm also upgraded the platform’s IO. The Snapdragon X2 Elite will support up to three USB 4.0 40Gb/s ports, and it features twelve PCIe Gen 5 lanes plus four PCIe Gen 4 lanes. In terms of storage, dual NVMe drives or UFS 4 will be supported, along with SD cards.

Security And Remote Management With Snapdragon Guardian

There is a gauntlet of security related features present on the Snapdragon X2 Elite too, including side-channel mitigations, control flow integrity measures, and a dedicated random number generator per CPU cluster. Qualcomm notes that the Snapdragon X2 Elite is not susceptible to attacks like PACMAN, Augury, GoFetch and others that have plagued recent processors.Notably, the Snapdragon X2 Elite supports secure state EL3, which is the highest and most privileged level of execution in the Armv8-A architecture. It runs exclusively in the secure state and is responsible for managing the transition between secure and non-secure enclaves. In addition, the Snapdragon X2 Elite supports Cryptographic Extensions and Control Flow Integrity (with pointer authentication, branch target ID, etc.). It also has Speculation-Barriers and RCTX restriction of context instructions (Restriction by ConTeXt).

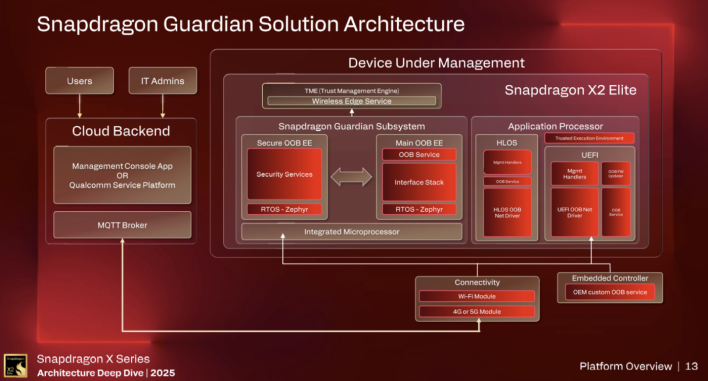

Snapdragon Guardian is a new feature coming to the platform that’s akin to Intel vPro or AMD’s PRO features. Snapdragon Guardian gives users the ability to remotely manage a PC from anywhere with a working internet connection, and to troubleshoot, track / locate, lock, or wipe the system. Snapdragon Guardian works with Wi-Fi, but some systems may also feature a basic, low-power 4G cellular modem as well, dedicated for use with Snapdragon Guardian. In other words, it won’t provide a general data connection for the PC; it’s strictly for Guardian. Another interesting point about Snapdragon Guardian’s dedicated 4G model is that it will only add a nominal amount of cost to a system and apparently won’t require a monthly connectivity fee.

Like previous-gen chips, the Snapdragon X2 Elite features an Always-On Subsystem. It operates in an ultra-low power state and maintains essential functions during device suspend and sleep states. It handles power and resource control and dynamically manages power delivery, activating subsystems only when necessary. It also oversees clocks, voltages, and memory activity of various IP blocks to minimize power consumption. The Always-On Subsystem enables rapid shifts between low-power and high-performance modes, using hardware-based controls to accelerate state transitions.

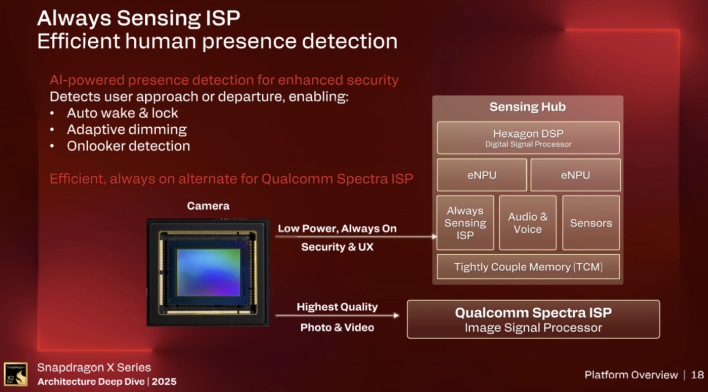

The Qualcomm Sensing Hub is present in the Snapdragon X2 Elite as well. The Qualcomm Sensing Hub offloads sensor tasks to a low power island for more efficient processing. It enables user experiences (like wake on voice, presence detection, etc.) with minimal impact to battery life. The Sensing Hub has access to a system’s cameras, speakers, mics, and various other sensors, but it also accepts input data from Wi-Fi and Bluetooth and can be used for location tracking.

Qualcomm Snapdragon X2 Elite Imaging, Video And Display Details

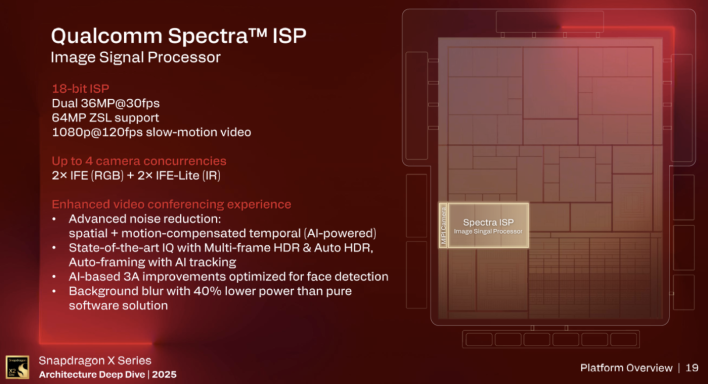

Like all of Qualcomm’s modern mobile processors, the Snapdragon X2 Elite features an integrated Spectra ISP (Image Signal Processor) to process and enhance camera data. The one present on the Snapdragon X2 Elite is an 18-bit ISP with support for dual 36MP recording at up to 30 frames per second. It also offers Zero Shutter Lag support with sensors up to 64MP, 120FPS slo-mo recording at 1080p, and up to 4 conncurrencies, for example with 2 x IFE (RGB) cameras and 2 x IFE-Lite (IR) cameras. The Spectra ISP’s high performance, coupled with Qualcomm’s imaging and video know-how, means the platform will offer enhanced video conferencing experiences versus most other PCs, along with a number of other photo and video benefits.

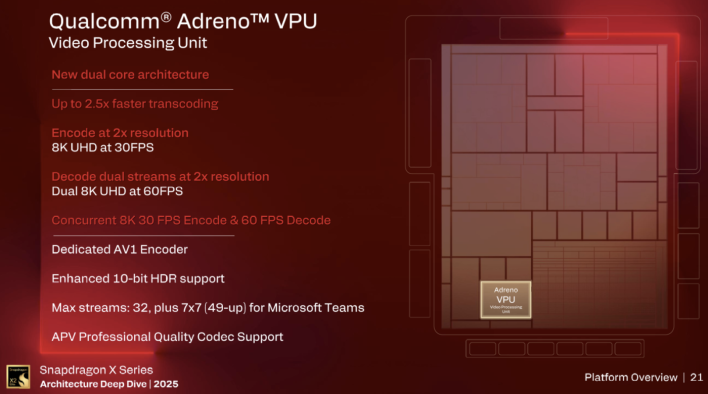

The Qualcomm Adreno VPU (Video Processing Unit) on the Snapdragon X2 Elite has a dual-core architecture and supports video encoding up to 8K 30FPS, as well as dual stream decode of 8K 60FPS streams, which is double the previous-gen. It also features a dedicated AV1 encoder, which the original X Elite lacked.

The Adreno DPU (Display Processing Unit) in the Snapdragon X2 Elite supports four 4K displays at up to 144Hz refresh rates, or alternatively, four 5K displays at up to 60Hz. The DPU also offers HDR support and advanced color management, scaling and sharpening, and smoother gaming animation thanks to variable refresh rate support.

Snapdragon X2 Elite CPU Microarchitecture Details

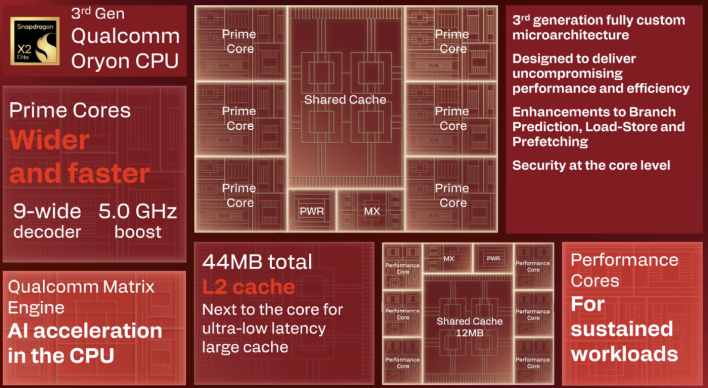

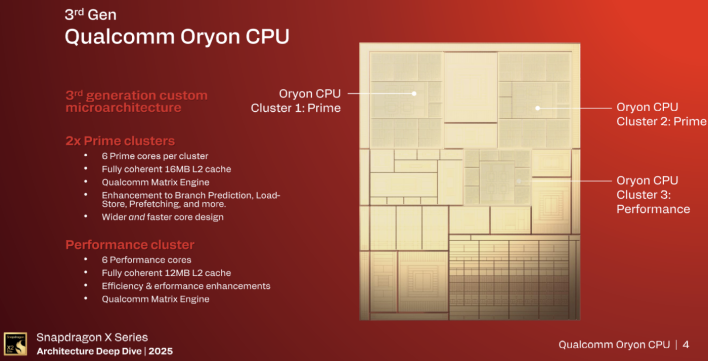

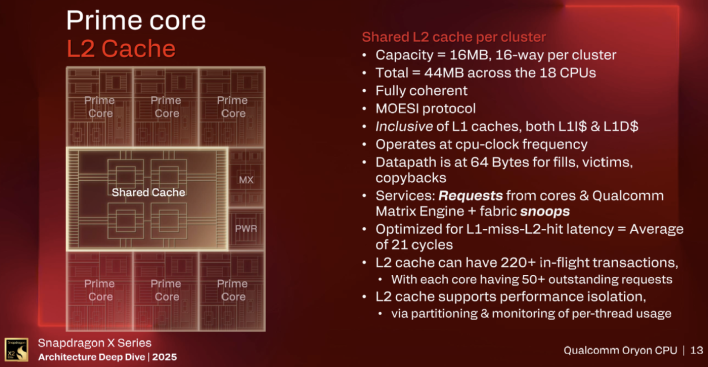

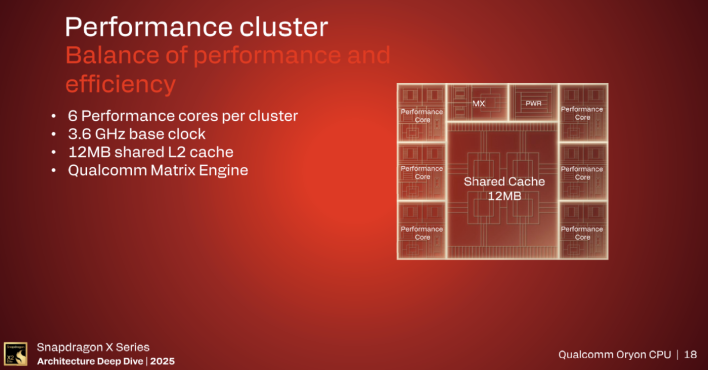

As mentioned previously, the Snapdragon X2 Elite features up to 18 CPU cores in the design. That's two Prime clusters and one Performance cluster, with 6 cores per cluster. Each Prime core cluster has a fully coherent 16MB shared L2 cache and Qualcomm matrix engine; the Performance cluster has 12MB of L2, but the Performance-cluster cores are also narrower, with fewer execution pipes, a shallower OoO execution window, and smaller TLB sizes. All of the cores are based on the latest iteration of Qualcomm’s 3rd-generation Oryon architecture, which is generally wider and faster than the previous-gen. The updated cores feature enhanced branch prediction, more load-store bandwidth, and enhanced prefetching among numerous other updates.

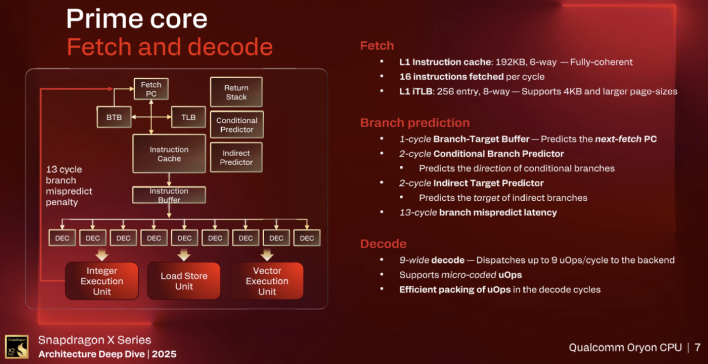

The Prime cores feature 192KB of total L1 cache, with 6-way full coherence. They support 16 instruction fetches per cycle and have a 256 entry L1i TLB, with 8-way coherence and support for 4K and larger page sizes. The updated branch prediction in the Snapdragon X2 Elite has a 1-cycle branch target buffer, with 2-cycle conditional branch prediction, and a 2-cycle indirect target predictor, which predicts the target of indirect branches. The design has 13 cycle mispredict latency.

The Prime cores support 9-wide decode and can dispatch up to 9 uOps per clock. The design also supports micro-coded uOps for efficient packaging of operations in the decode phase. The Snapdragon X2 Elite has wider rename to match the decode width, allowing it to process a larger number of instructions simultaneously in a single clock cycle. There are separate physical register spaces for integer, vector, predicate, and status registers. The integer and vector rename spaces can each hold 400+ registers and have checkpoints for fast rewind and restoration of the renamer on branch mispredict flushes.

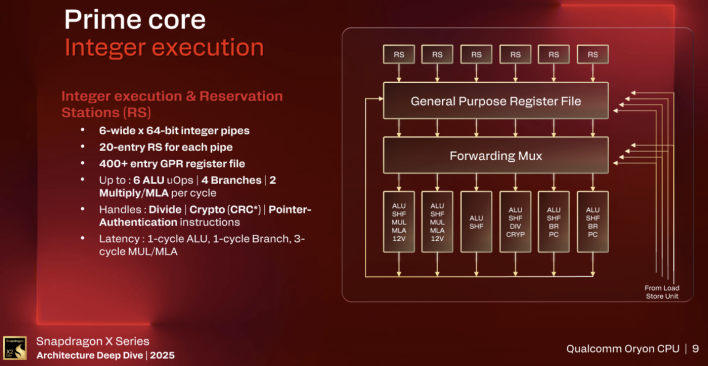

Integer Execution is 6-wide with 64-bit integer pipes, with a 20-entry Reservation Station (RS) for each pipe. There’s a 400+ entry General Purpose Register (GPR) register file, and support for up to 6 ALU uOps, with up to 4 branches, and 2 multiply/MLA per cycle.

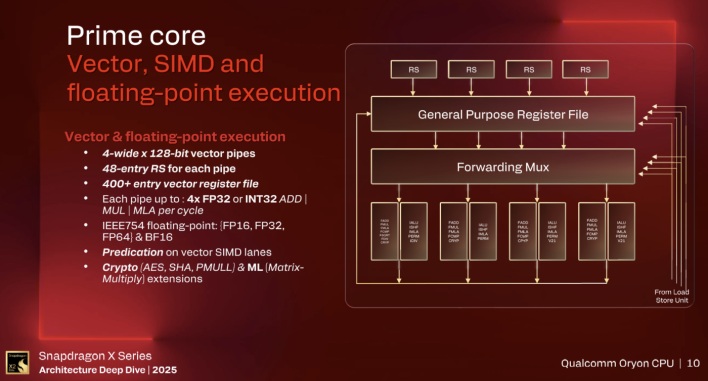

Vector, SIMD, and FP execution is 4-wide with 128-bit vector pipes, with a 48 entry RS for each pipe and a 400+ entry vector register file. Each pipe supports up to 4 x FP32 or Int32 ADD – MUL – MLA per cycle. The processor naturally supports IEEE 754 floating point formats, including FP16, FP32, FP64, and BF16 data types, and predication on vector SIMD lanes.

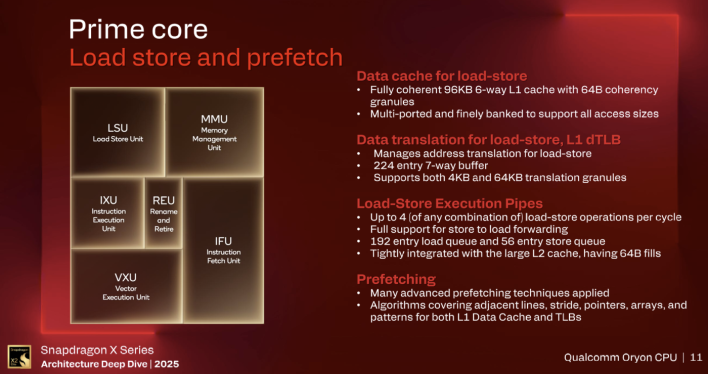

The data cache for load store and prefetch is a fully coherent 96K 6-way L1 cache with 64B coherency granules that’s multi-ported and finely banked to support all access sizes. The L1 dTLB manages address translation for load-store operations and features a 224-entry 7-way buffer, with support for both 4KB and 64KB translation granules. Any combination of up to 4 load-store operations are supported per cycle, with full support for store to load forwarding. There’s a 192-entry load queue and 56-entry store queue, that’s tightly integrated with the L2 cache.

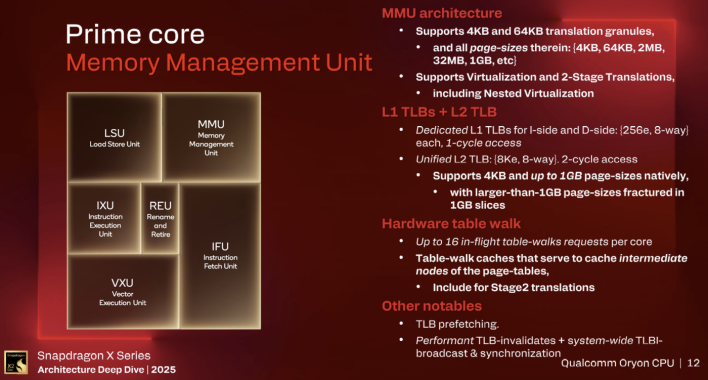

The MMU supports 4K - 64KB translation granules with virtualization support for 2-stage translations, including Nested Virtualization. There are dedicated L1 TLBs for I-side and D-side, with support for 256-entries (8-way each, 1 cycle access) and a unified L2 TLB with support for 8K-entries (8-way, 2 cycle access) and support for 4KB and up to 1GB page sizes natively, with page sizes larger than 1GB fractured in 1GB slices.

As mentioned, each Prime cluster has 16MB of L2 cache. That’s 16-way per cluster for a total 44MB across all 18 CPU cores (the Performance cluster has 12MB L2). The L2 is fully coherent, uses the MOESI protocol (Modified, Owned, Exclusive, Shared, Invalid), and is inclusive of L1 caches, both L1i and L1d. The L2 operates at the CPU clock frequency and the datapath is 64-bytes for fills, victims, and copybacks. The L2 is also optimized for L1-miss-L2-hit latency, which averages 21 cycles. That’s actually higher than the previous-gen’s 17 cycles, and is due to the increased cache sizes and core counts. The L2 cache can have 220+ in-flight transactions, with each core having 50+ outstanding requests

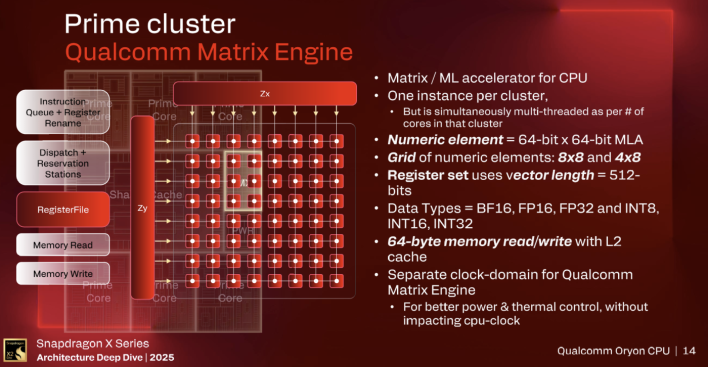

The CPU core clusters in the Snapdragon X2 Elite are also the first Qualcomm CPUs that come with their own matrix accelerator. There is one Matrix Engine per cluster, shared by all of the cores per cluster. The Matrix Engine supports 64-bit × 64-bit MLA, and is fully SIMD across integer and floating-point data types. it also supports a grid of 8x8 and 4x8 numeric elements, and the register sets use a vector length of 512-bits. BF16, FP16, FP32 and INT8, INT16, and INT32 data types are all supported. Furthermore, the Matrix Engines also operate on separate clock domain for better power and thermal control, as well as less impact on the CPU clock.

The Performance core cluster is scaled down somewhat from the Prime cores, to offer a better balance of performance and energy efficiency – sometimes operating below 2W. There’s also 6-cores per performance cluster, with 12MB of shared L2 cache, a single Matrix Engine, and a lower 3.6GHz base clock. The Performance cores have a similar out-of-order microarchitecture, but narrower, with fewer execution pipes, shallower OOO execution window, and smaller caches and TLBs, as noted above.

Snapdragon X2 Elite: Adreno X2 GPU Details

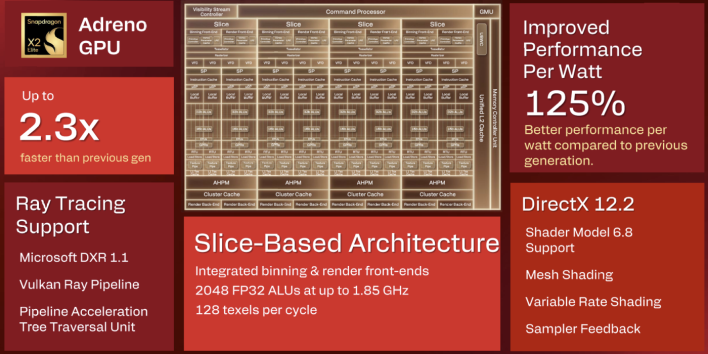

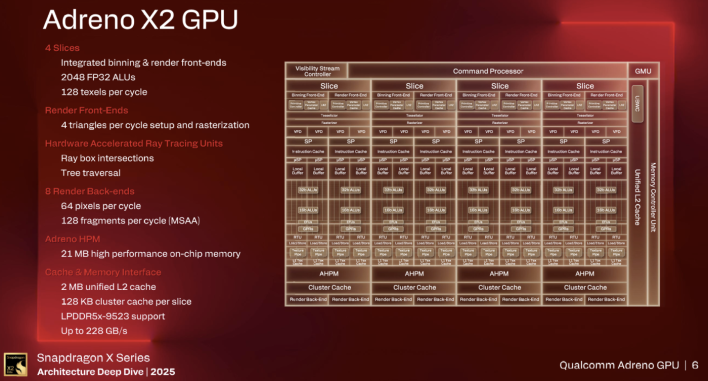

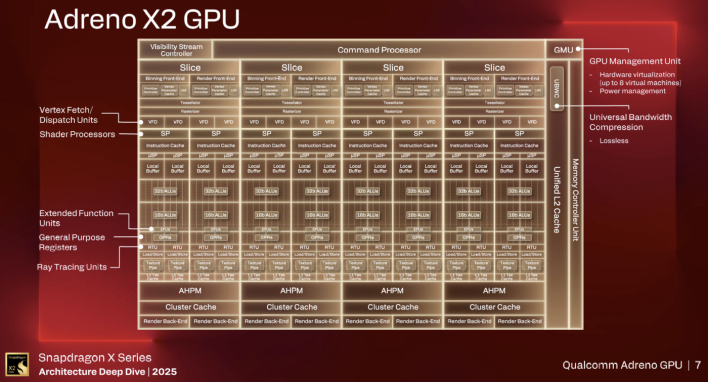

There are two Adreno X2 GPU configurations coming with the Snapdragon X2 Elite; a 4-slice design in the 18-core parts and a 3-slice design in the 12-core part (dubbed Adreno X2 90 and Adreno X2 85). The GPU is reportedly as much as 2.3X faster than the previous gen, while also up to 125% more energy efficient.

The Adreno X2 has full support for DirectX 12.2 Ultimate and Shader Model 6.8, with mesh shading, fully-compliant Variable Rate Shading (VRS), and support for sampler feedback. According to Qualcomm, the Adreno X2 offers up to 33% more performance than the previous generation in terms of its ALUs and backends, with proportionally increased efficiency, and the GPU has been redesigned and optimized to hit higher clocks. It’s also linked to higher speed memory in this platform; Qualcomm claims it’s the fastest GPU the company has ever built.

The Adreno X2 is part of the eighth generation of Adreno products, which was designed completely in-house. Like other modern GPUs, the Adreno X2 is composed of smaller units, linked together to produce a GPU of a certain size and performance level. The top-end configuration is composed of four slices versus three in the previous-gen, with integrated binning and render front ends, 2048 FP32 ALUs across all 4 slices, and support for up to 128 texels per cycle. There are two shader cores inside each slice.

The render front ends support 4-triangles per cycle and there are new, higher-performing Ray Tracing units – 16 in total on the 4-slice design – with 2 RTUs per shader pipe (2 pipes per slice). The RTUs feature full DXR 1.1 and Vulkan Ray Pipeline support, as well as enhanced pipeline acceleration in the tree traversal unit.

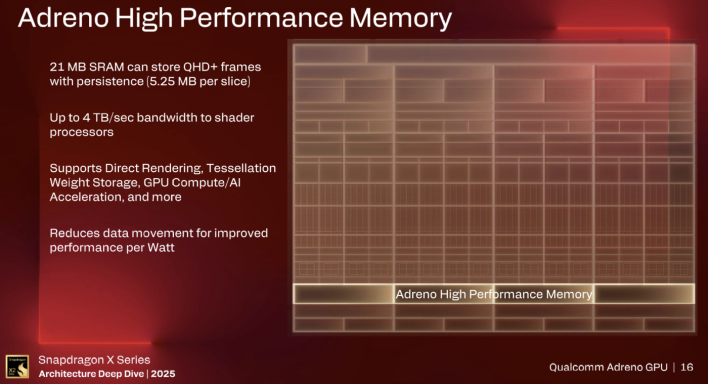

There are 8 render back ends in the design, which support 64 pixels per cycle, and 128 fragments per cycle for MSAA. There’s also a total of 21MB of high-performance on-chip memory in the GPU, dubbed Adreno HPM, which is segmented into 5.25MB per slice. The Adreno HPM offers up to 4TB/s bandwidth to the shader processors and supports direct rendering, tessellation, weight storage, and GPU compute / AI acceleration. Like AMD’s Infinity Cache and the large L2 cache on NVIDIA's Ada and Blackwell GPUs, Adreno HPM reduces data movement across the memory interface, for improved performance per watt and higher effective memory bandwidth.

Indeed, the Adreno X2 has double the L2 cache (2MB unified L2) of the previous-gen, with 128KB cluster cache per slice, and support for LPDD5X up to 9,533 MT/s for a peak bandwidth of 224 GB/s over the 192-bit memory interface.

There’s a GPU Management Unit preset on the Adreno X2 that monitors activity, measures temperatures, and even knows leakage (identified at wafer sort). The GMU creates a model of power being used and controls power management (voltage and frequency) to throttle the GPU, or power it off completely when not needed. The GMU also handles hardware virtualization.

Qualcomm says that the Adreno X2 offers faster geometry processing than the previous-gen, with improved throughput and high-polygon performance. It offers 4X faster primitive rates and 4X the vertex processing per slice. The design is also vastly improved for small draw calls. The wave size is 64-wide now (it was just 12-wide on X1), with 128KB per uSP for GPRs – it used to be 96KB on the Adreno X1. The larger cache allows for more waves in flight, or more complex waves that can take full advantage of the shader units.

In terms of GPGPU workloads, the Adreno X2 has native driver support for WCR (Windows Copilot Runtime), BF16 support, local memory broadcast, and general shuffles, which allows full shuffling between the threads.

On the software side, Qualcomm states it is planning to move to a monthly release cadence, although it didn’t announce when that would begin. As it stands now, the Adreno X2 driver has native support for DX 12.2, OpenCL 3.0 and SYCL, and a Native Vulkan 1.4 driver is coming in Q1 '26. Qualcomm is also working toward full kernel-level anti-cheat compatibility and hopes that by the launch of Snapdragon Elite X2 all major anti-cheat technologies will be natively supported.

Qualcomm Hexagon NPU Enhancements

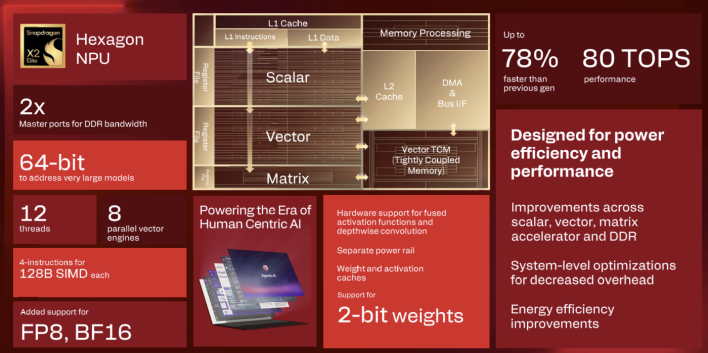

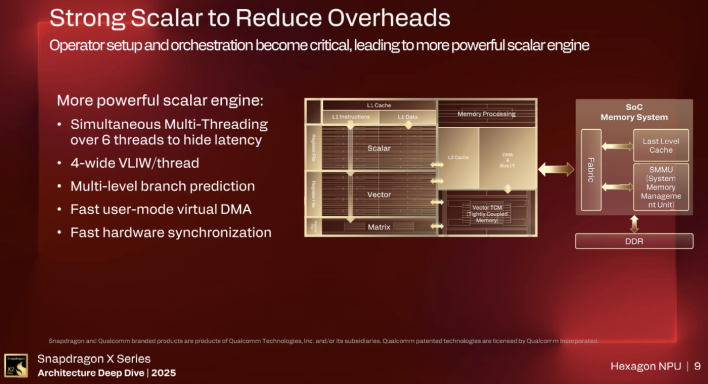

The Snapdragon X2 Elite is also outfitted with multiple NPUs. There’s a dedicated, larger Hexagon NPU, based on a 6th Generation (NPU6) core design, that offers up to 80 TOPs, which makes it up to 78% faster than the previous gen while also being more power-efficient. The Hexagon NPU has 2× master ports for increased memory bandwidth, with 64-bit DMA support for large models, and support for up to 12 threads. The end result is a 143% increase in scalar performance and a 127% increase in bus bandwidth.In terms of vector processing, the Hexagon NPU has 8 parallel engines that support for up to four 128b SIMD instructions each, with support for FP8 and BF16 data types. According to Qualcomm, the 6th Gen NPU in the Snapdragon X2 Elite offers a 143% increase in vector throughput over the previous gen.

For matrix processing, the Hexagon NPU has support for 2-bit weights, support for FP8 and BF16, and hardware support for fused activation functions and depthwise convolution. The Hexagon NPU also operates on its own power rail. Qualcomm is claiming a 78% increase in matrix throughput with the design.

In addition to the large Hexagon NPU, there are dual micro embedded eNPUs on a low power island in the Snapdragon X2 Elite, that offer a staggering 6× higher performance than the X1. The eNPUs are always-on alternatives to larger hexagon NPU, and have access to 9MB of cache on the low power sensing hub.