Intel Plans Z990 And Z970 Chipsets For Next-Gen Nova Lake Desktop CPUs

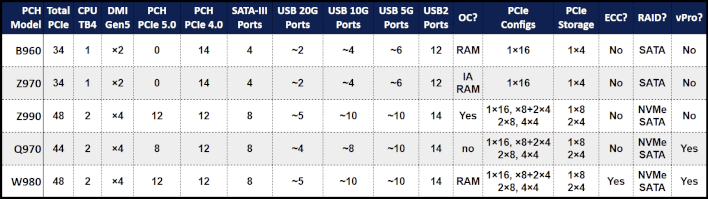

Starting off with the biggest leak, we have what appear to be full specifications of the chipsets for Intel's Nova Lake processors. This information comes from Jaykihn, who has been remarkably reliable and relatively forthcoming with Intel leaks, specifically. The chart below pretty much tells the story, but we can sum it up for you: five chipsets, ranging from B960 to Z990, but unusually excluding any H-series chipsets yet still including both Q970 and W980 models. The presence of two Z-series chipsets is also fascinating, especially given that they differ in surprising ways.

Typically, when you see "Z" on an Intel chipset, that's the highest-end model. The Z970 here looks much closer to the B960, though; indeed, they share virtually all specifications save for that the Z970 will allow "IA" overclocking; that's not a typo, but rather it's the term Intel uses internally to refer to x86 CPU cores. ("Intel Architecture"). In other words, Z970 will apparently let you overclock the CPU cores where B960 won't. BCLK overclocking is still limited on the Z970 though, and it will be interesting to see if that extends to clock rates like the CPU ring bus, the die-to-die interconnect, and the uncore clock.

Z990, Q907, and W980 also simply get a whole lot more connectivity than the other two chipsets. Z990 has a whopping 48 PCI Express lanes, with 24 of those coming from the chipset. Likely as a result, the "DMI" link between the CPU and the chipset (or "PCH" as Intel calls them) is twice as wide on Z990, Q970, and W980, allowing the CPU to pull twice as much data through the chipset. Other striking product segmentation selections include just a single M.2 slot on the B960 and Z970 platforms and the continued blocking of multi-bit ECC on consumer platforms.

Then we have this bombshell from kopite7kimi. He's more known for his NVIDIA leaks, but frankly, this isn't completely implausible (despite the hilarious reaction from Kepler in the thread.) If you can't see the image, he says "The power consumption of a full-load NVL-K is over 700 watts."

He clarifies in replies that this refers to the dual-compute-tile version with 52 total CPU cores, and also that this is with power limits removed, not a standard TDP rating. But he also says that "you can't expect a low PL2," and that "350-400W" is "totally not enough." He claims the chips' compute tiles will be manufactured on TSMC N2P, which is interesting considering what Intel has said about its 18A yields.

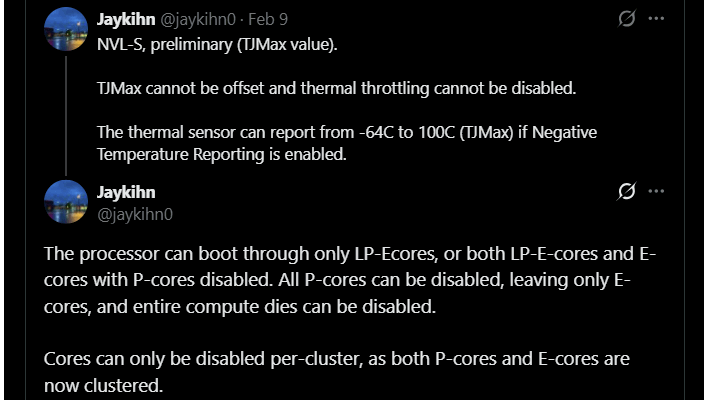

It really puts this other post from Jaykihn into a stark light, if true. Jaykihn writes that Nova Lake desktop CPUs cannot have their "Tjmax" temperature offset. That's the CPU junction temperature, or essentially, the temperature inside the processor, and extant Intel processors support applying an offset to this value so that you can encourage thermal throttling earlier or delay it to higher temperatures if you don't care about the longevity of your CPU.

Apparently, this won't be possible with Nova Lake, and he goes on to explain that this applies to both positive and negative offsets, as well as that the Nova Lake Tjmax value is fixed at 100℃—not particularly controversial in and of itself, but it's interesting to see that Intel is locking the processors down in this specific fashion.

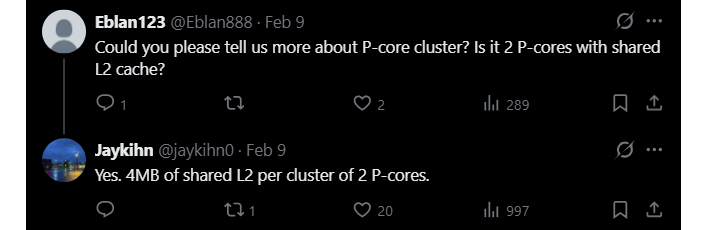

Finally, we have this remark from Jaykihn. He says that Nova Lake processors can boot through LP-E cores, through LP-E and E-cores, or with all cores active. Apparently entire compute tiles can be disabled in firmware, but that's not the interesting part of this post. Instead, the interesting part is the reveal that, on Nova Lake, P-cores will apparently be clustered as E-cores have been in the past. In a reply, he states that each pair of P-cores shares 4MB of L2 cache.

This is a really interesting design decision that smacks of AMD's "Clustered Multi-Threading" designs—yes, the much-maligned "construction core" lineage. Those chips shared more than just cache between the two halves of each "module", though. This makes sense when you consider that Intel has removed Hyper-Threading from its client hardware; perhaps this is a way to achieve similar multi-threaded gains without sacrificing single-threaded performance. 4MB of L2 cache is certainly quite beefy.

If even half of these rumors are true, Nova Lake is still shaping up to be an incredibly spicy launch for Intel. Hopefully the firm can get these chips fabbed and shipped by the end of the year; it'd be a shame if we had to go this whole year without any novel processor launches.