AMD Zen 6 Gaming Chips Rumored To Top 6GHz And Flex Up To 240MB Of L3 Cache

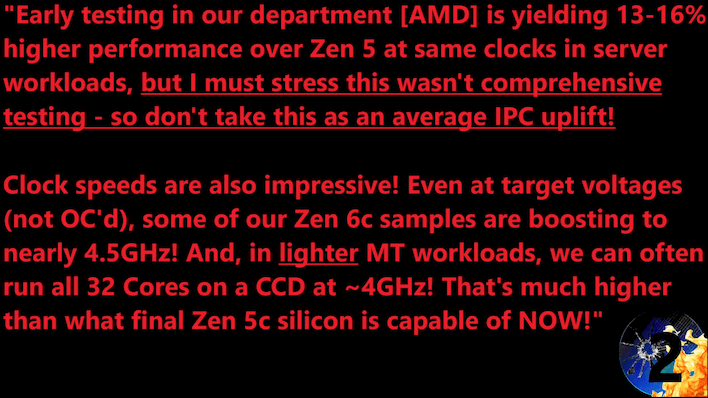

Now, the latest rumors regarding AMD's next-generation CPU core have hit, and they're looking pretty spicy. First up: clock rates. This one isn't strictly new; it was first leaked back in February. However, the same source has doubled down on the claims and says that 7 GHz isn't out of the question. He stopped short of saying that AMD CPUs definitively would reach 7 GHz, but did say that AMD's next desktop CPUs will beat 6 GHz, and "not 6.1 or 6.2 GHz."

If that sounds insane, remember that we're talking about a multi-node die shrink here, and furthermore, we're also looking at a move to GAAFET fabrication (although the TSMC N2 process in use won't have back-side power delivery like Intel's 18A.) AMD's current processors already hit 5.7 GHz without overclocking; 6 GHz isn't particularly hard to achieve; even 6.4 GHz is barely more than a 10% increase in clock rates.

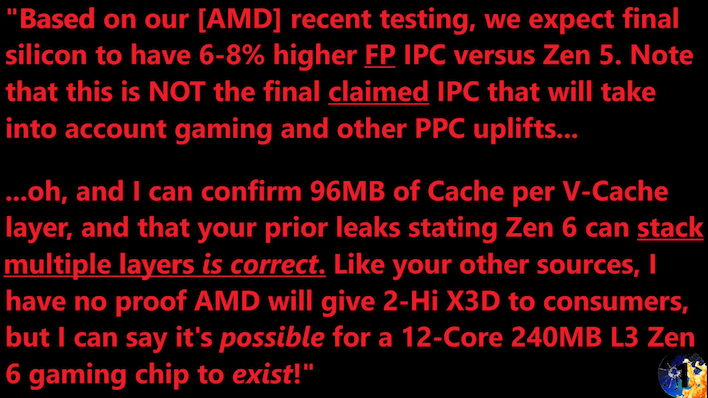

However, that clock rate bump will apparently also come along with a nice little bump to IPC, as well. YouTuber Moore's Law is Dead quotes "one of [his] best AMD sources" as noting that final Zen 6 silicon will have "6-8% higher floating-point IPC versus Zen 5." That's not exciting, but remember that floating point math is only one piece of the puzzle. There are other features coming in Zen 6 that may improve performance per clock in interesting ways, like by reducing core-to-core latency. More on that in a moment.

The other half of this leak, as you can see, is the leaker's anonymous source's claims regarding the next generation of 3D V-Cache. As a refresher, 3D V-Cache is AMD's term for its stacked cache technology where it pairs the logic chip of a processor with a separate piece of silicon that is mostly just SRAM. This, historically, triples the L3 cache available to that chiplet's CPU cores. Well, Zen 6 is getting a bump to 48MB of L3 cache per CCD to maintain the cache-per-core ratio, and thus, the 3D V-Cache stacks for Zen 6 are also getting a bump to 96MB.

That's not the end of the story, though. It was rumored in prior generations that AMD could feasibly ship a 3D V-Cache CPU with multiple stacks of cache applied. AMD has never shipped a processor this way to date, but MLiD's source claims that AMD has verified this capability on Zen 6 parts. Doing so would result in a processor with some 240 MB of L3 cache on a single CCD, or around 20 MB of L3 cache per individual Zen 6 CPU core. This would be an incredible amount of CPU cache, and it would likely have a deleterious effect on cache access latency, which is exactly why AMD probably won't do it. The thought is tantalizing, though.

Other key details about Zen 6 that Moore's Law is Dead has previously leaked include that the chips will purportedly include "bridge dies" between the CCDs holding the CPU cores and the cIOD, and that the Zen 6 mobile processors will be chiplet designs for the first time. The latter is simple: the successor to Gorgon Point (itself a refresh of Strix Point) will use the same CCDs as the other Zen 6 processors, meaning no more "C" compact cores, and no reduction in L3 cache compared to the desktop CPUs. It also means that AMD's APUs could receive 3D V-Cache for the first time, which is a fascinating prospect.

The other detail is arguably more impactful for most users, though, and it was initially leaked by Everest (@Olrak29_). By "bridge dies", they're probably referring to is the use of TSMC's "Local Silicon Interconnect" (LSI) technology. You can reasonably think of LSI as TSMC's version of Intel's Embedded Multi-Die Interconnect Bridge (EMIB). Essentially, rather than using wires in an interposer, connections between chiplets are done using a bridge die with multiple routing layers. This provides a solution that is more compact, more efficient, and faster; if true, this could mean memory latency and core-to-core latency on Zen 6 processors could be as low as it has ever been.

Is all of this true? There's no telling. Moore's Law is Dead has been known to spread bunkum from time to time, but he also has been known to pick up exclusive leaks years ahead of anyone else. Everything we've talked about today seems entirely plausible, aside from the idea that AMD will actually ship a gaming CPU with 240MB of L3 cache. Still, Zen 6 does look incredible for gamers. Reduced memory latency due to LSI, bumps to both IPC and clock rates, an extra four CPU cores per CCD, and an accompanying increase in L3 cache are all welcome.