Intel Penryn and Nehalem Details Emerge

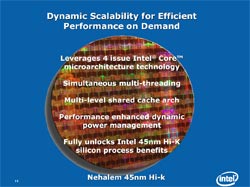

After Penryn and the 45nm High-K silicon technology introduction comes Intel's next-generation microarchitecture, dubbed Nehalem, which is slated for initial production in 2008. With Nehalem Intel plans to deliver further performance and energy efficiency gains, and more performance-related features and capabilities for new and improved applications.

Below is a list of the new initial disclosures Intel has made regarding the Nehalem microarchitecture:

|

|

|

|

According to Intel, Nehalem is the company's first truly dynamically scalable microarchitecture and Intel considers the Nehalem system and interconnect architectures the biggest system architecture transition since the introduction of the FSB.

Nehalem is a new microarchitecture that leverages much of the technology introduced with the Conroe. With Nehalem, however, each processor core is capable of executing two threads simultaneously, similar to the way Hyper-Threaded worked. Nehalem also features a multi-level shared cache architecture, with the last level of cache being shared, which balances on-die resource across multiple threads.

Nehalem is also natively architected to take full advantage of 45nm, and with Nehalem will come a totally new system architecture and a next-gen platform architecture. There will be different sockets across different market segments with configurations capable of handling 1 - 16+ threads (8 Cores) and 1 - 8+ cores (16 threads).

Perhaps in its biggest departure from current products, Nehalem will feature a new link-based architecture, with some configurations sporting integrated DDR3 memory controllers, and integrated graphics for some market segments. Intel was unclear how the memory controllers and integrated graphics would be configured, but it was said that the graphics core will reside in the processor socket, not necessarily on the same die though. Intel did not disclose how many links would be part of the architecture, core configurations, etc. They simply wanted to describe some of the possibilities of the new platform and system architectures.

According to Intel, Nehalem is on track for '08 and designs featuring 8 cores are already underway.

Discuss This Article In Hothardware's PC Hardware Forum Now!