IDF Preview - Rambus Debuts PCI Express Gen2

Rambus Debuts PCI Express Gen2 Solutions

Rambus Showcases Silicon Verified Demo

Compliant with Gen2 Revision 0.5 Specification for PCI Express

Seamlessly integrated digital controller and PHY solution for next generation PC and peripheral interconnect...

Los Altos, California, United States - 09/25/2006 Rambus Inc. (Nasdaq: RMBS), one of the world's premier technology licensing companies specializing in high-speed chip interfaces, today announced the availability of its Gen2 Total Solution silicon demo, a complete communications interface solution featuring an integrated digital controller and PHY implementation for the next generation of PCI Express(R) technology. At a 5.0 Gbps transfer rate, Gen2 offers twice the bandwidth performance of its predecessor. The Gen2 demo will be introduced at the Intel Developer Forum (IDF), September 26-28, 2006; Moscone Center, San Francisco, CA.

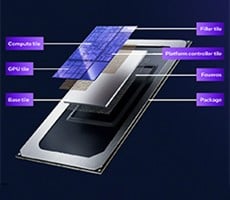

Rambus Gen2 is a complete communications interface solution for the expected PCI Express Base Specification, revision 2.0 requirements. Rambus PHYs support the PMA and PCS layers of the PCI Express specification. Rambus digital controllers are available as root complex, switch port, end point and hybrid (end point/root complex) device types. The advanced features, bandwidth and scalability of Gen2 meet the high performance requirements of next-generation graphics, desktop, mobile, server, and consumer platforms.

"The Rambus Gen2 PHY represents the latest technology advancement in PCI Express, supporting up to 160 Gbps bandwidth," said Rich Warmke, Director of Marketing for Platform Solutions at Rambus Inc. "In addition, the Gen2 PHY functions as a multi-protocol cell for Gigabit Ethernet, XAUI and double XAUI applications."

The Gen2 demo shows a PCI Express PHY implemented in TSMC's 90nm GT process technology. Demo features include:

- 5.0 Gbps transfer rate, shown in x1 lane width

- "Board-to cable-to board" data

- Scope showing PHY eye diagram

- DLL and TL transactions demonstrated with LeCroy protocol analyzer

- Digital controller for expected PCI Express Gen2 specification (Data Link Layer and Transaction Layer) demonstrated in FPGA

RAMBUS PCI Express Gen2 Total Solutions Product Brief

The availability of Gen2 SerDes essentially means double the interface bandwidth for this point-to-point interconnect technology in next gen Computing architectures. Gen2 will also come with a whole host of new features targeted at things like QoS and other bandwidth provisioning technologies. Word is that Gen2 capable chipsets and end-points (graphics processors, controllers, etc) probably won't make their way into next gen architectures and market-ready products until sometime in the second half of '07. -HH