Odds are that every PCI Express device you have in your machine right now uses PCIe 4.0 or an older standard. We have PCIe 5.0 support in

the latest desktop machines, but there are no PCIe 5.0 graphics cards yet, and while PCIe 5.0 storage is available (and fast!), it's also relatively expensive and offers little practical benefit for most users. However,

the PCIe 6.0 spec is out, and so is

the 7.0 draft spec.

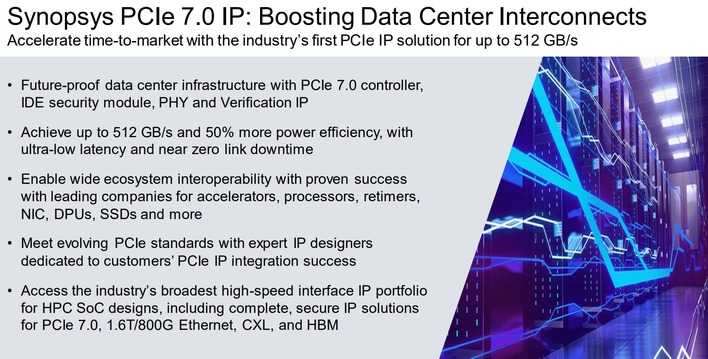

We haven't heard much about PCIe 6.0 adoption, but it may be the case that some vendors skip over it entirely because Synopsys is already offering PCIe 7.0 IP for licensing to customers that feel the need for speed. How much speed? Up to 512 GB/second across two directions on an x16 link. That's a lot of bandwidth.

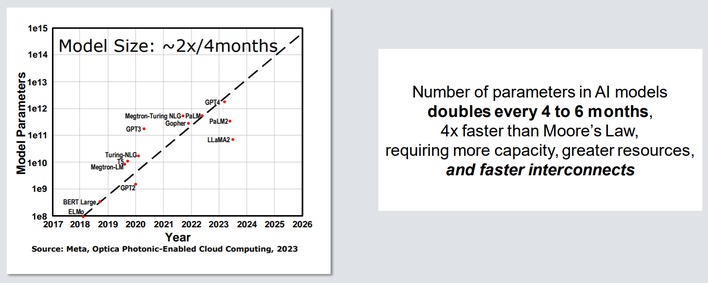

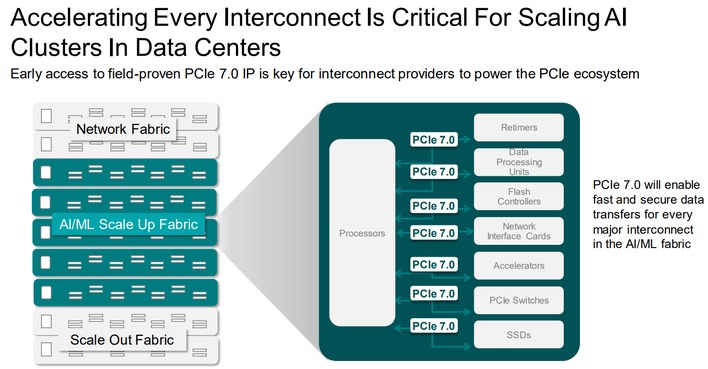

If PCIe 4.0 is just fine for gamers, you might be wondering what the hurry is to move to newer and faster interconnects. The answer, of course, is for enterprise computing, particularly hyperscale operators

looking to train AI ever faster and more efficiently. Efficiency is the name of the game with PCIe 7.0, after all; Synopsys says that its PCIe 7.0 IP is "50% more efficient" than PCIe 5.0 on a per-lane basis.

That means it still uses more power as the transfer rate is four times as high, but 2.67x the power for four times the bandwidth is a pretty solid trade-off in our books. If only we could see

scaling like that for CPU or GPU clock rates. A single lane of PCIe 7.0 can move data at 16GB/second in one direction, which is more than enough bandwidth for lots of devices, making bifurcation support ever more useful.

In fact, PCIe 7.0 is so fast that it can actually make sense to use it as an interconnect for additional memory, allowing chips to be connected to large amounts of

Storage-Class Memory (SCM) or plain old RAM in external banks. If you're like me, think back to the ancient

expanded memory cards of yore, just many millions of times more capacious and performant.

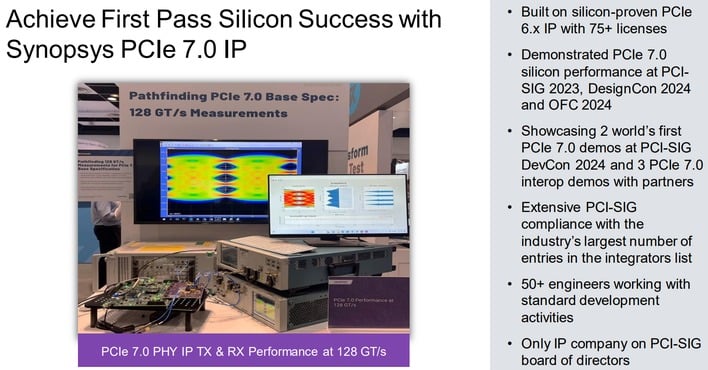

Synopsys says that it is the first to market with a complete PCIe 7.0 IP solution, including controller, integrated security module, physical interface (PHY), and verification IP. Hopefully the availability of

a complete implementation for licensing this early means that we'll see PCIe 7.0 devices hit the consumer market sooner than later.

Synopsys also says that it will be demonstrating this technology live at

PCI-SIG DevCon 2024 in Santa Clara on June 12th and 13th. If you are silicon engineer, you probably won't want to miss it.