RISC-V Silicon Successfully Fabricated on Intel 3 In Major Chip Milestone

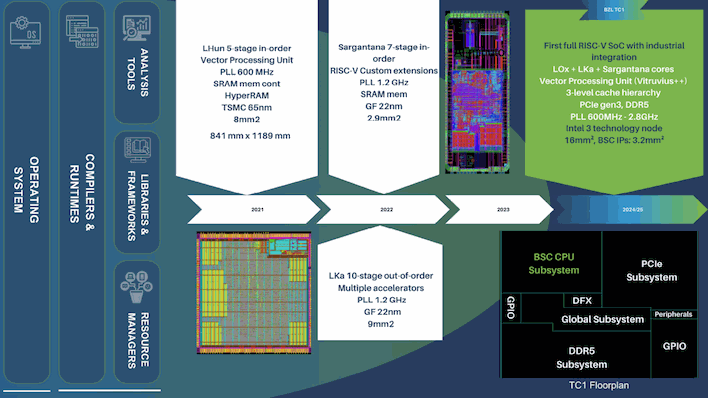

The chip, known internally as "TC1" and evaluated on Intel's Hawk Canyon V2 board, was designed as part of Europe's broader effort to reduce reliance on non-European processor technologies for high-performance computing. The project is linked to the European Processor Initiative (EPI), which aims to develop homegrown processors for future European supercomputers and industrial systems.

Fabricated on Intel 3, TC1 integrates a heterogeneous architecture composed of three independent tiles, each built around a different RISC-V processor core: Sargantana, Lagarto Ka (with vector processing unit), and Lagarto Ox. The CPU subsystem occupies just 3.2mm² of a tiny 15.2-mm² die, which also includes high-speed interfaces such as PCIe Gen5 and DDR5. For perspective, an eight-core AMD Zen 5 CCD is ~71mm², and that chiplet still requires a separate I/O die.

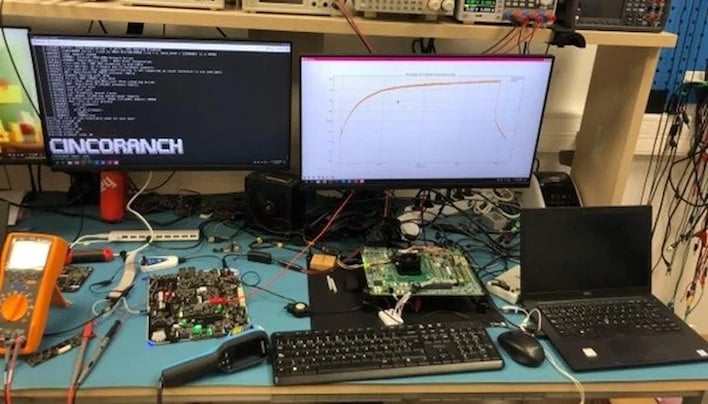

Because Intel 3 was not accessible to external entities during early design stages, BSC validated its RTL code using TSMC N7 as a proxy node before final implementation by Intel. Following fabrication, the lab successfully booted Linux on the chip in May 2025, validated first by Intel and then reproduced in BSC's own labs. A subsequent batch of 500 chips demonstrated high functional yield, with most units successfully bringing up all three integrated processors. The silicon has been shown to operate at up to 1.25GHz, exceeding conservative pre-tapeout estimates.

Some folks might sneer at it, but Intel 3 itself is an advanced EUV-based node that presents a significant refinement over Intel 4. While obviously not the company's newest process tech—Intel 18A now represents the leading edge both at Intel and elsewhere—it remains a high-density, modern logic node comparable in class to TSMC's N5/N4 family. In other words, this is not trailing-edge experimentation; it is serious, contemporary silicon.

Still, it's important to clarify that RISC-V processors today are not direct competitors to flagship x86 or Arm cores from Intel, AMD, Apple, or Qualcomm at the high-performance desktop or premium mobile tier; the ecosystem, tooling maturity, and architectural tuning of those incumbents reflect decades of optimization. Fortunately, that's not the immediate goal here. For BZL and its partners, the objective is to prove that European-designed, open-ISA processors can be implemented on cutting-edge fabrication technology and brought to life in real silicon. Successful Linux boot, functional validation across hundreds of units, and early power and thermal characterization represent exactly the kind of post-silicon milestones required before scaling to more ambitious HPC-class designs.

The broader significance is that, for Europe, Barcelona Zettascale Labs' TC1 is a tangible step toward technological autonomy in high-performance computing. For Intel, it demonstrates that its foundry business can absolutely support advanced external customers in complex heterogeneous designs. No single prototype establishes sovereignty or disrupts global CPU markets, but bringing up modern RISC-V silicon on an advanced node is a concrete, measurable achievement regardless.