AMD Zen 6 CPUs Look Poised For A Major Interconnect Upgrade

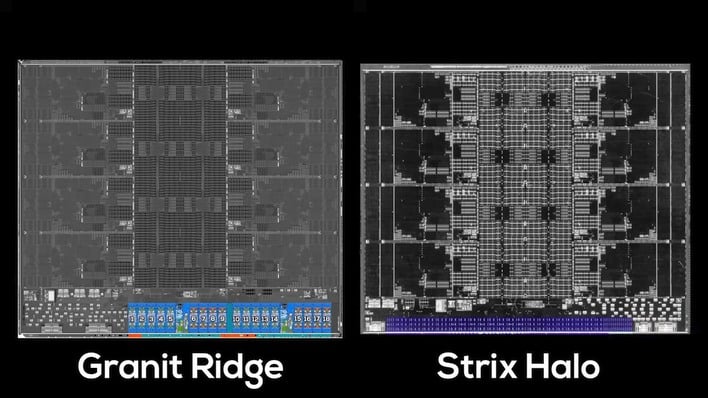

High Yield, an English-language technology YouTuber from Germany that we've reported on before, has an insightful observation: AMD's Strix Halo chips, the Ryzen AI Max 300 series, don't use Infinity Fabric between the CCDs and the cIOD. Instead, they actually use a much denser and much more parallel connection that skips the serialization step required for Infinity Fabric. This makes routing the link much more difficult, but it also radically improves both performance and power efficiency.

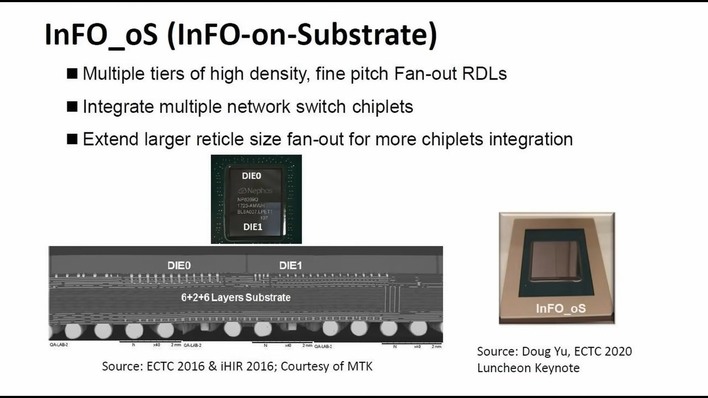

The specific link that AMD is using on Strix Halo hasn't been disclosed, but it's almost assuredly an implementation of TSMC's InFO-oS technology, which stands for "Integrated Fan-Out - On Substrate". In essence, there is a "Re-Distribution Layer" (RDL) between the silicon chips and the organic substrate—the small PCB that makes up the "body" of the processor package—that serves to offer a direct connection between chips. Thanks to this RDL, it's possible to use a massively-parallel connection to wire chips together. This eliminates the need for serialization, effectively making the two chips function just like a single piece of silicon.

The YouTuber feels that AMD's use of InFO-oS on Strix Halo was for two reasons: first, as a power-saving measure for the thirsty Strix Halo mobile processors, but more strategically, as a trial run for its Zen 6 processors. Anyone who has overclocked a Ryzen desktop processor will tell you that performance is much more likely to be bottlenecked by memory latency or fabric bandwidth than by the CPU clock, and Intel has seen similar effects with its Arrow Lake CPUs; the Core 200S Boost Mode's main function was to overclock the Die-to-Die fabric by 60%.

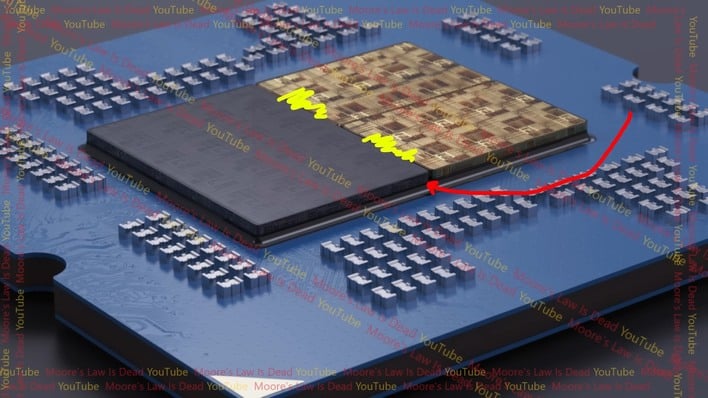

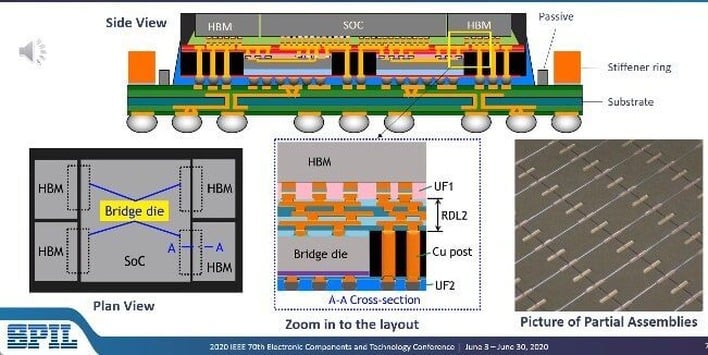

High Yield isn't actually the first person to make a very specific guess about what AMD will do with the interconnect on its its next-generation processors, though. Some seven months ago, contentious leaksman Moore's Law is Dead claimed that AMD will instead make use of "bridge dies" on at least some Zen 6 processors. Specifically, he remarked that he believes AMD will use a technology called "Fan-Out Embedded Bridge" (FOEB) from a supplier known as Siliconware Precision Industries (SPIL).

FOEB is a little more complicated than InFO-oS, but it's a similar fundamental idea, and it can reasonably be seen as a mid-step between InFO-oS and another TSMC technology, known as InFO-LSI. We've actually reported on this topic before. In short, the idea is that AMD might use "bridge dies" to connect its chiplets, rather than a pure RDL solution as with InFO-oS. This has significant advantages in terms of both latency and throughput, as it allows AMD to clock the interconnect higher and it also allows for a wider interconnect. However, it's also more expensive and more complex to manufacture, which may be why High Yield is putting his bets on InFO-oS.

It may actually be the case that AMD will use both technologies. Its client products may not need the benefits offered by SPIL's FOEB and TSMC's InFO-LSI, and may indeed use the simpler InFO-oS, while the company deploys the more advanced bridge-based interconnects on its professional and enterprise-oriented products, like EPYC processors and Instinct accelerators. AMD has already used similar technologies in places besides Strix Halo, including the high-end RDNA 3 GPUs (and their "Infinity Fanout Links") as well as extant Instinct products.