AMD Reveals New Zen 6 Details In First Official Document

The document, titled "Performance Monitor Counters for AMD Family 1Ah Model 50h–57h Processors," was posted publicly on Wednesday, December 17th, 2025, and is dated December 12th, 2025. It was first spotted by well-known x86 microarchitecture enthusiast InstLatX64 on Xwitter, who highlighted several intriguing new features buried in the performance counter listings.

Although the document focuses on performance monitoring rather than marketing features, it still reveals three major points of interest: FP16 execution support, a new Memory Profiler IBS mechanism, and evidence of up to six integer scheduler domains.

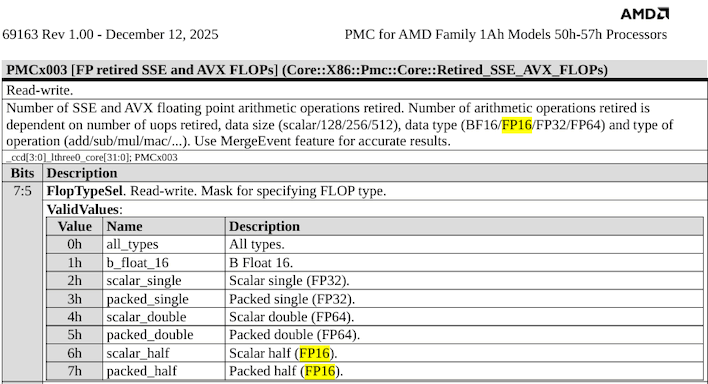

FP16 Execution Support For Faster AI Processing

We already suspected that this support was on the way, because it was included in patches for the open-source GNU Assembler, Gas. This is unequivocal confirmation direct from AMD, though. The formal appearance of FP16 support in Zen 6 CPU performance counters suggests fully native FP16 handling on the CPU side, offering up to double performance in AI inference, certain types of media processing, and scientific workloads that can tolerate lower precision.

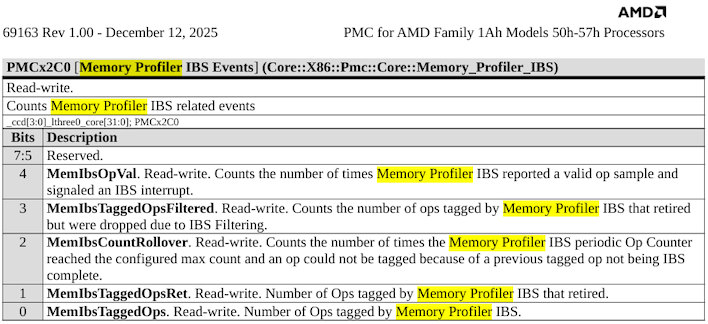

New "Memory Profiler" IBS Events

What's new here is that the Memory Profiler IBS appears to be a distinct sampling mechanism focused specifically on memory behavior rather than a simple extension of existing IBS features. The counters describe tagged instructions, retirement tracking, rollover behavior, and filtering, all of which are signs of dedicated hardware designed to observe how individual instructions interact with the memory subsystem.

This suggests that Zen 6 places a stronger emphasis on detailed, instruction-level memory profiling, likely reflecting the growing importance of memory latency, bandwidth, and queue contention in modern workloads. Both gaming and AI are as often as not bound up on memory performance before compute or I/O, and this change implies that AMD is giving developers the tools they need to truly optimize memory access on Zen 6. This is probably only of real interest to compiler authors and hyperscalers, but it's potentially the most important of the three additions.

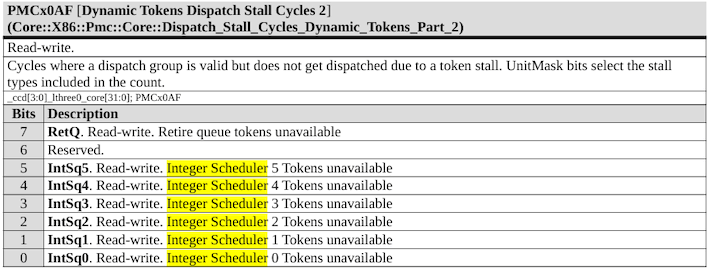

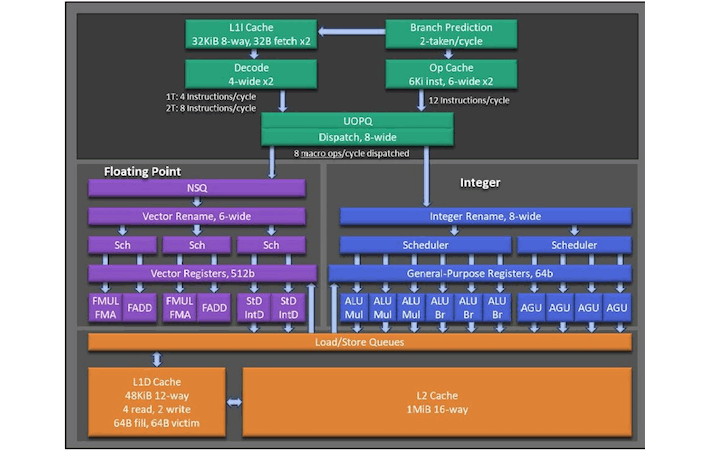

Evidence of Six Integer Schedulers

This isn't necessarily a pure gain, though; if it were, Intel and AMD would have never moved to unified scheduling. Partitioned schedulers require good dispatch heuristics in hardware, better compiler awareness, and potentially, dynamic steering or even migration between scheduler domains. In short, it's simply a much more complex design that historically, hasn't been known to be a profitable trade-off, but it's a whole new world of workloads and processor design these days.

AMD hasn't officially detailed Zen 6 yet, and performance counter documentation doesn't necessarily map one-to-one with final retail silicon. Still, this is the earliest concrete, first-party technical evidence of Zen 6's internal design. Between FP16 support, enhanced memory profiling, and a potentially reworked integer backend, the Zen 6 "Morpheus" architecture appears poised to be more than a simple incremental update.

That lines up with earlier leaks and rumors claiming that "Zen 6" will be as much of a jump from Zen 5 as "Zen 2" was from the original Zen design. Intel's Nova Lake is looking to be a similarly sizable step forward from Arrow Lake, so we might be in for quite a battle of giants late next year.