Intel Nova Lake May Abandon AVX-512 And These Other CPU Instruction Sets

Well, that's almost assuredly not happening, as it turns out. We know that because, as Phoronix reports, the GNU Compiler Collection (GCC) has added support for targeting Nova Lake with code compiles. As part of that support, the GCC patch has to enumerate all of the Instruction Set Extensions supported by the Nova Lake processors, and here's that list:

MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AES, PREFETCHW, PCLMUL, RDRND, XSAVE, XSAVEC, XSAVES, XSAVEOPT, FSGSBASE, PTWRITE, RDPID, SGX, GFNI-SSE, CLWB, MOVDIRI, MOVDIR64B, WAITPKG, ADCX, AVX, AVX2, BMI, BMI2, F16C, FMA, LZCNT, PCONFIG, PKU, VAES, VPCLMULQDQ, SERIALIZE, HRESET, AVX-VNNI, UINTR, AVXIFMA, AVXVNNIINT8, AVXNECONVERT, CMPCCXADD, AVXVNNIINT16, SHA512, SM3, SM4, PREFETCHI

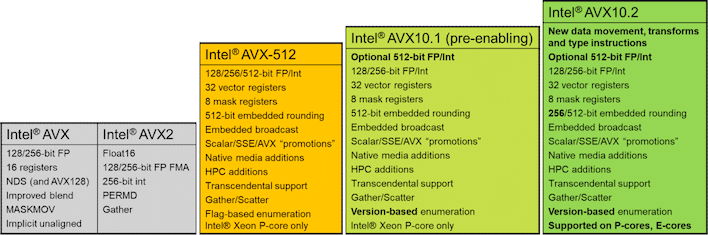

Observant readers will have already picked out the distinct lack of AVX-512, AVX10, AMX, or APX identifiers. In other words, the only new instruction set extension that Nova Lake will support over Arrow Lake (and indeed, Panther Lake) is the PREFETCHI instruction block that originates with Granite Rapids Xeon processors. This extension adds two new instructions that are specifically for prefetching instruction data (read: code) into the cache hierarchy. They can help with AI and gaming workloads, but of course, the code has to be compiled with this support, meaning that it's unlikely app developers will bother until years after the extension is ubiquitous.

It's arguable whether this really matters, of course. While AVX-512/AVX10 instructions are very important for scientific and high performance computing (HPC) workloads, they simply aren't present in most consumer tasks. A few things, like console game emulation, compression, and specific encryption workloads can benefit from it. Otherwise, its loss is essentially irrelevant to Nova Lake, and in any case, modern Intel CPUs are fast enough to run PS3 games far faster than an original PS3 ever did without AVX-512, so even the RPCS3 argument doesn't hold much water. AMD only equips its CPUs with AVX-512 because it re-uses the same chiplets for its EPYC server CPUs, after all.

As Phoronix explains, the patch was merged in yesterday, and will be part of the GCC 16.1 stable release that's planned to hit early next year—although you can of course grab the source yourself from the GCC Git if you want to start coding for Nova Lake. Hopefully this is the only disappointing news we hear about Intel's next desktop CPUs.