Intel To Detail 3D Chip Packaging For Next-Gen Meteor Lake And Arrow Lake CPUs

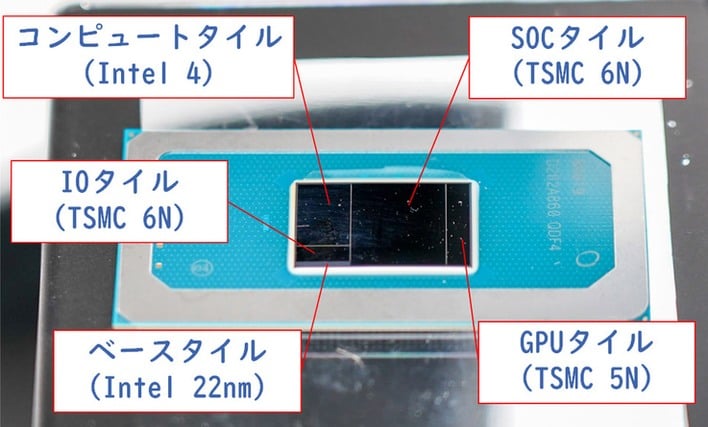

Foveros is the name for Intel's innovative chiplet technology. It differs from traditional 3D stacking in that it enables logic-on-logic stacking, meaning that you can have disparate types of processors stacked on one another. Intel will be making use of that capability for its next-next-gen Meteor Lake processors, which will be its first chiplet-based (or "disaggregated") processors.

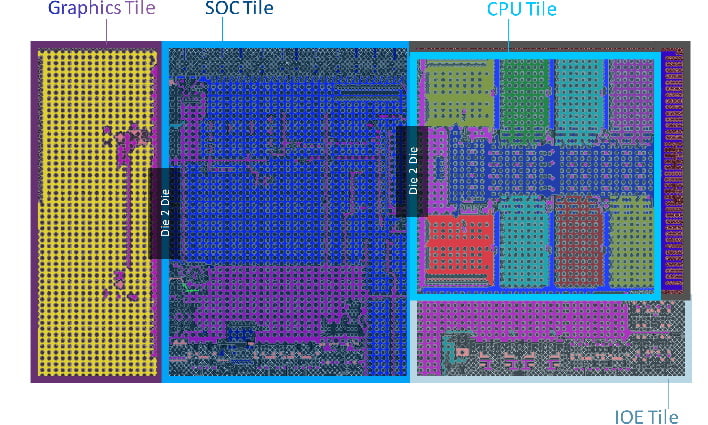

In preparation for its talk at Hot Chips 34, Intel held a media roundtable where it handed out (among other things) this nifty little graphic that elaborates on what the disparate dice in Meteor Lake processors actually do. Leakers and enthusiasts had pretty much put this information together already, but it's always nice to have official confirmation.

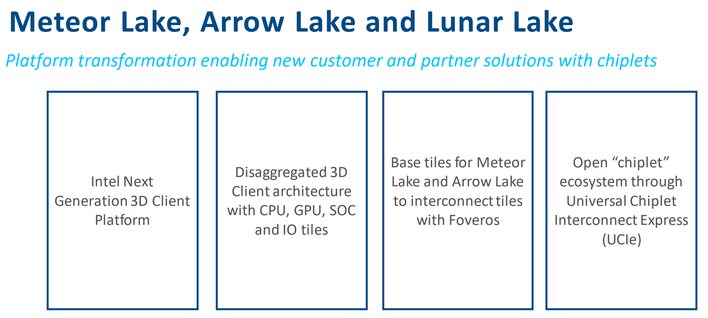

The actual talk, titled "Meteor Lake and Arrow Lake: Intel Next Gen 3D Client Architecture Platform with Foveros," takes place tonight at 5:00 PM Pacific time. However, there were already a few interesting details divulged during the media roundtable.

Intel's Boyd Phelps specifically said that Meteor Lake is on schedule, which gave some in the media cause to exhale after rumors came out last week that Intel had cancelled some of its 3nm orders with TSMC. An Intel roadmap from back in February gave the impression that Intel could be using TSMC's 3nm process for Meteor Lake.

This use of a "base tile" is interesting, and it's apparently one of the things we'll hear more about at tonight's presentation, along with additional details regarding Intel's disaggregated design strategy as well as more information about Universal Chiplet Interconnect Express, or "UCIe". UCIe is intended to be an open standard for die-to-die connections on chiplet processors.

The aforementioned Boyd Phelps commented in the roundtable that UCIe won't be used in Meteor Lake nor in the 15th-gen Arrow Lake processors, but that it will come in "products after Arrow Lake." We'd assume that that's going to be the previously-revealed Lunar Lake, which is also mentioned in the header of the tile above.

It's possible that the presentation will be overwhelmingly a rehash of details we already know, but we suspect there might be a nugget or two of gold in the splash of details. We'll be paying attention to the presentation this afternoon, and we'll make sure to let you know if Intel reveals anything of note.