Intel CEO Hints At Stacked Cache On Future CPUs Sometime After Meteor Lake

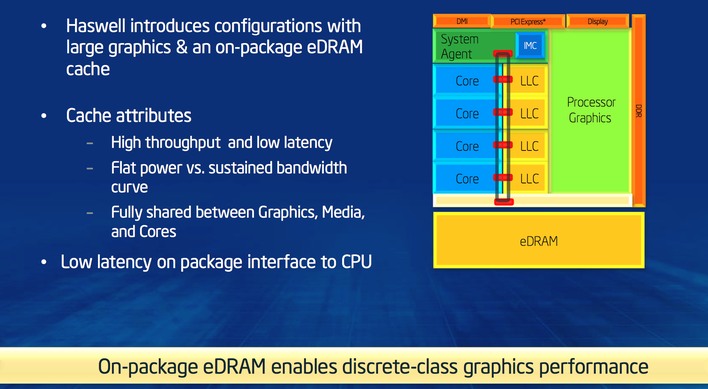

Intel's no stranger to chip stacking, nor to the idea of add-on cache for CPUs. In fact, the company did it first, back in 2013 with Haswell CPUs that included the "Crystal Well" 128MB eDRAM cache die on the package. It worked like a System Level Cache, in that it could cache memory for any part of the SoC. It improved the integrated graphics performance of CPUs so-equipped dramatically, but later, it also improved the CPU-only performance of the desktop Core i5-5675C and Core i7-5775C when they were equipped with discrete GPUs.

Gelsinger's response to the question was long, but here it is, cut slightly for brevity:

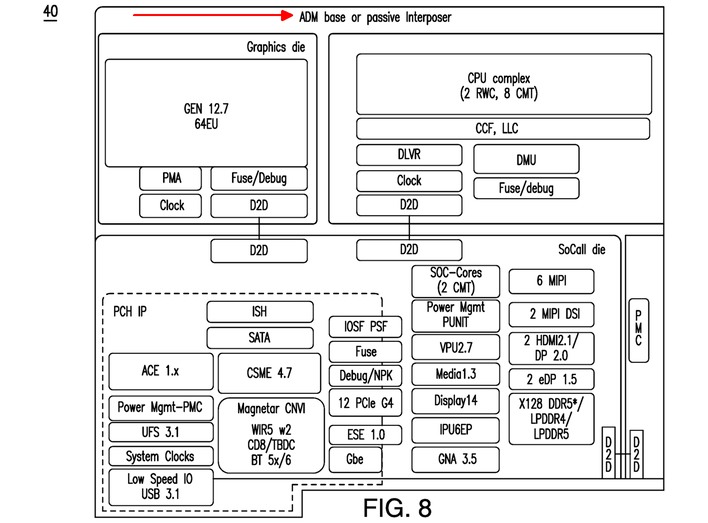

"When you reference V-Cache, you're talking about a very specific technology that TSMC does with some of its customers as well. [...] That particular type of technology isn't something that's part of Meteor Lake, but in our roadmap, you're seeing the idea of 3D silicon where we'll have cache on one die, and we'll have CPU compute on the stacked die on top of it, and obviously using EMIB and Foveros we'll be able to compose different capabilities."

Gelsinger went on to say "we feel very good that we have [...] advantages for 3D stacking for both little die as well as for very big packages for AI and high-performance servers as well. [...] We'll be using those for our products, as well as presenting it to the foundry customers." This would seem to state outright that Intel plans to make use of stacked memory technologies in both its CPU and GPU products, including the massive many-tile behemoths in its Data Center GPU Max range.

We're curious to see if those technologies and ideas will filter down into the consumer-facing Arc Graphics product line. AMD achieved a humongous performance and efficiency leap from RDNA to RDNA 2 by applying liberal amounts of "Infinity Cache" to its GPU architecture. It will be fascinating to see if Arc can shore up its middling efficiency in coming generations by making use of extensive caching.