PCI Express 7 Draft Spec Targets Glorious 512GB/s Of Bandwidth For Next Gen Devices

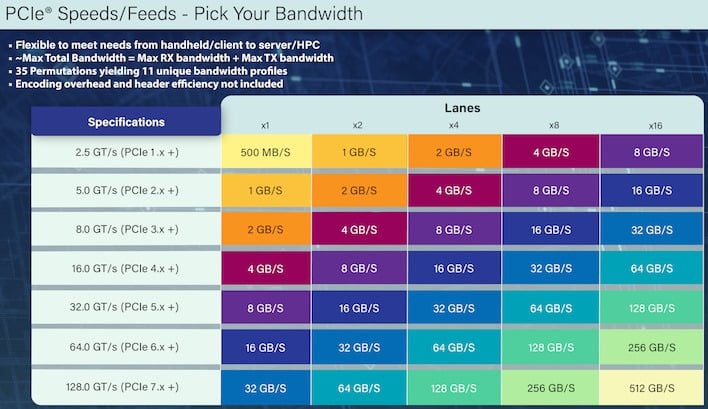

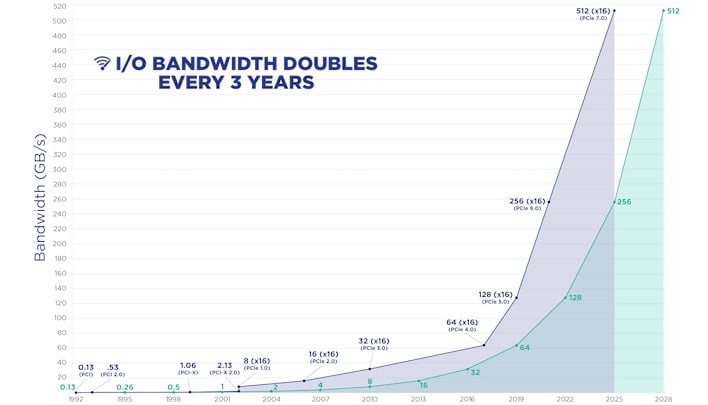

Of course, both are much faster than the PCIe 4.0 and 5.0 connections available in current-generation systems, which run at 2GB/sec and 4GB/sec per direction per lane, respectively. Even those transfer rates are astonishing when you start piling up the lanes; a typical PCIe 5.0 M.2 socket has some 16 gigabytes per second of full duplex bandwidth. An equivalent PCIe 7.0 device would theoretically support up to 64GB/second transfers.

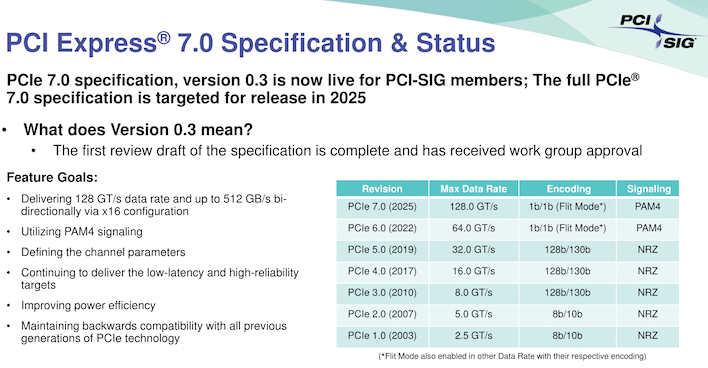

PCIe 7.0, in contrast, still uses PAM4 signaling, but now doubles the clock rate once again. This is going to make some serious manufacturing challenges for companies building PCIe 7.0 hardware, as they need to maintain extremely clean signaling at ludicrously-high clock rates to make a good PCIe 7.0 connection.

Besides extremely-high-speed networking and massive storage arrays, there are also products like Compute Express Link (CXL) that rely on the PCIe physical layer to do their thing. CXL aims to be, among other things, an interface for storage-class memory, and memory interfaces are usually a lot faster than current-gen PCIe.

The current publication is PCIe 7.0 draft version 0.3, and the specification is available to members of PCI-SIG. If you're of a mind to read the specification, you'll have to be a member, or get it form someone who is. For the rest of us, well—PCI-SIG probably won't publish the final PCIe 7.0 specification until 2025, and we likely won't see hardware with the interconnect until 2027 or later.