Leaked AMD Mendocino Block Diagram Reveals Its Unique Chip Architecture

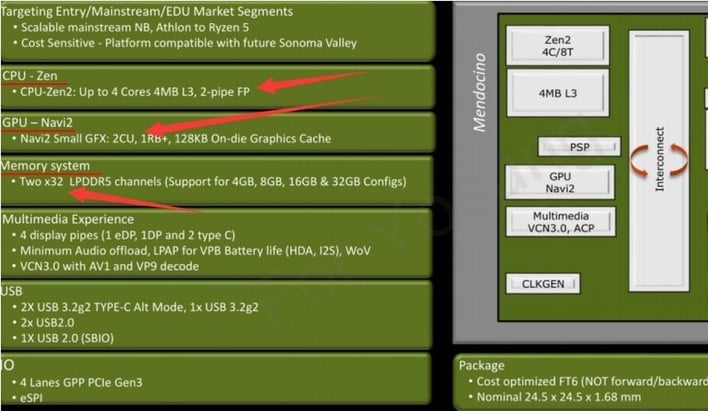

Furthermore, the slide above—unearthed by Olrak (@Olrak29_ on Twitter)—seems to indicate that Mendocino's Zen 2 cores aren't exactly the same as those featured in Aerith and other products based on Zen 2, like the Xbox Series X, PlayStation 5, and of course, the company's Ryzen 3000-series processors.

For starters, the L3 cache on this chip has been slashed from 16MB (per-CCX on other Zen 2 parts) to just 4MB. It also seems to have had half of its floating-point compute ability lopped off. Zen 2 parts normally have four floating-point pipes, but this diagram, if legit, seems to indicate that Mendocino's cores will only have two. That will seriously hurt performance in crunchy, branchy floating-point code, but the markets these chips are meant for don't do a lot of that kind of computing anyway.

So saying, even if a Mendocino device were equipped with extremely fast LPDDR5-6400 memory, it's only looking at about 51 GB/sec of memory bandwidth. That's barely more than half of what the Steam Deck manages thanks to its full-sized 128-bit memory bus. That 51 GB/sec has to be shared with the four Zen 2 cores, too, and their small cache means that they're going to have to dip out to main memory more often as well.

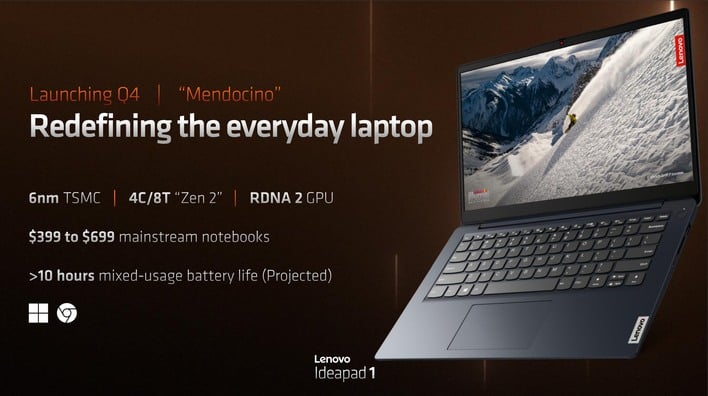

To summarize, Mendocino truly is a processor created to be as cost-effective as possible, just as Dr. Su said at Computex. It has cuts to its Zen 2 cores and their associated cache, it has a narrow memory bus to simplify product implementations, and it has an extremely tiny 2-CU RDNA 2 GPU, according to the leaked slide..

Despite all that, we're actually pretty confident that it will still perform well in its intended market of education and low-powered devices. We do have to admit that we're curious to see the impact of the incisions AMD made to cut costs, though. If we get our hands on such a system, we'll put it through its paces and report back.