Intel Panther Lake-H High-Res Die Shots Reveal 18A CPU Design

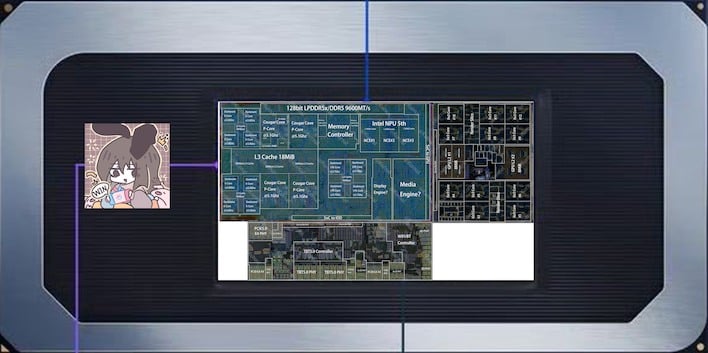

If you don't recall, Intel's Core Ultra 300 series can come in a variety of configurations ranging from one with just six CPU cores all the way to 16 CPU cores and 12 Xe3 GPU cores. The one that Kurnal has shaved the top off of appears to be the top-end configuration used in the Core Ultra X9 388H. He's ground down all three tiles used in the chip so that we can see the insides.

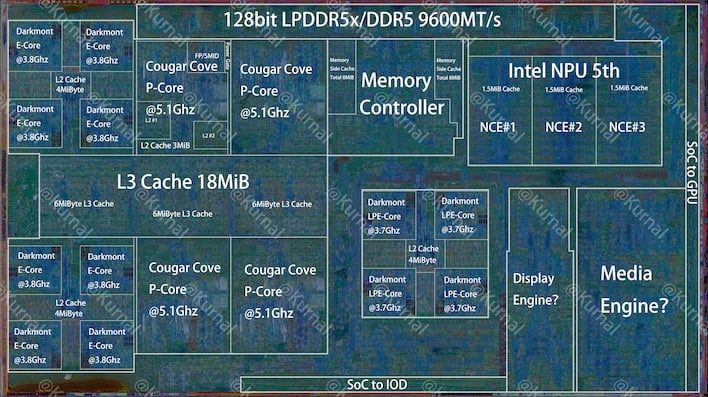

In this picture of the Panther Lake 16-core compute/SoC tile, the photo is quite blurry, apparently due to Intel's use of PowerVia back-side power delivery. Kurnal has labeled the 128-bit memory PHY and its associated controller, the 16MB of "Memory Side Cache" (effectively a system-level cache), the four Cougar Cove P-cores, the eight Darkmont E-cores, the 18MB of L3 cache that those clusters share, and then the separate cluster of four Darkmont LP E-cores.

The powerful Intel NPU takes up a huge portion of the die in the upper right, and then there are two large blocks that Kurnal has speculated may be the display engine and media engine. These blocks exist on the SoC tile so that the chip can shut down the GPU tile when it's not performing intense 3D graphics duties, saving quite a bit of power.

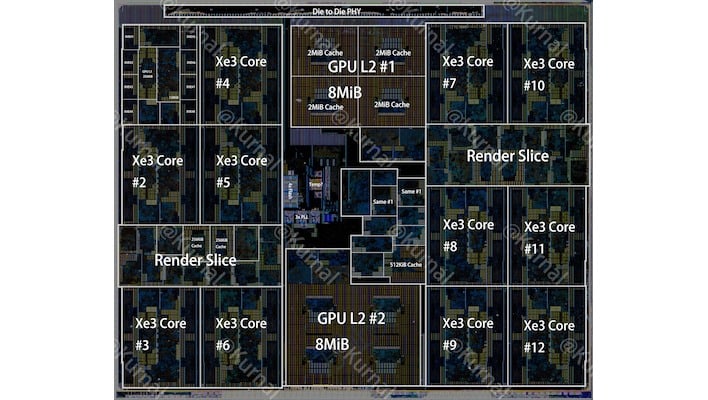

Speaking of that GPU tile, Kurnal was able to get a much clearer photo thanks to the fact that it's not fabbed on Intel's 18A process and thus doesn't use back-side power delivery (as 18A is the only process in the world with the tech, for now.) It's remarkable how much of the die is occupied by cache, but it's likely exactly that which allows the Arc B390 integrated graphics of the Core Ultra X9 388H to kick so much butt. If you haven't read our review yet, you should definitely check it out; it's super impressive.

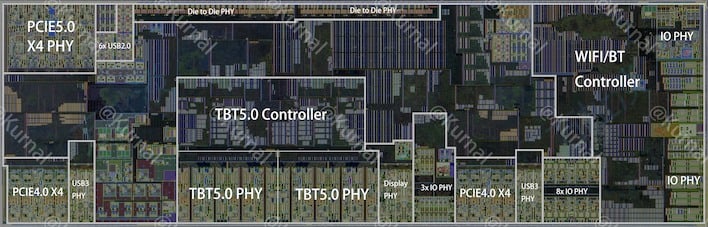

Finally, the I/O die hosts the majority of the off-chip I/O, including USB, PCI Express, Thunderbolt, Wi-Fi, and Bluetooth. Kurnal has the Thunderbolt interface labeled as Thunderbolt 5 here, but that's not correct; Panther Lake actually has Thunderbolt 4, not Thunderbolt 5. It's striking how much of the die the Thunderbolt interfaces take up; nearly a quarter of the entire I/O die is occupied by the TB4 physical interface and controller (at least, assuming Kurnal labeled it correctly.)

The combined view here lets you see the relative sizes of everything. A single Xe3-core is nearly the size of two Darkmont E-cores, and just one Cougar Cove P-core dwarfs nearly every other functional component in size despite being fabricated on the most advanced manufacturing process in the world (again, for now.)

Getting die shots like this requires destroying one of the processors in question, so our hats are off to Kurnal for taking one for the team to produce these cool photos. Head to his site if you want to see the photos in glorious 8K resolution.