Apple Reportedly Booked Majority Of TSMC's 2nm Chip Capacity To Get A Head Start

Let's back up a second. Current-generation processors are largely built on 4nm-class and 3nm-class technology, and the next jump is going to come from 2nm-class processes, of which there are four on the way: TSMC's N2, Intel's 18A, Samsung's SF2, and newcomer Rapidus' 2HP. Of those, Intel isn't taking external orders, Samsung isn't quite ready yet, and Rapidus isn't even planning to be be ready until 2027.

That leaves TSMC's N2 as the only 2nm-class fab available to fabless customers, yet one customer in particular (Apple, of course) is getting priority treatment. This isn't a surprise at all, since Apple has been TSMC's biggest customer for years, and furthermore, the company took upwards of half of TSMC's opening capacity at the 5nm and 3nm feature sizes, too.

TSMC has two separate fabs in Taiwan where it is doing 2nm production, with the northern fab in Hsinchu Baoshan reportedly being fully dedicated to Apple's new chips. Meanwhile, the southern fab in Kaohsiung is handling other customers, apparently including Intel. That runs contrary to earlier reporting that omitted Intel in a list of the first wave of TSMC 2nm customers, but to be clear, the source doesn't say that Intel is purchasing manufacturing capacity this year, only that it is seeking a tape-out on 2nm for future products.

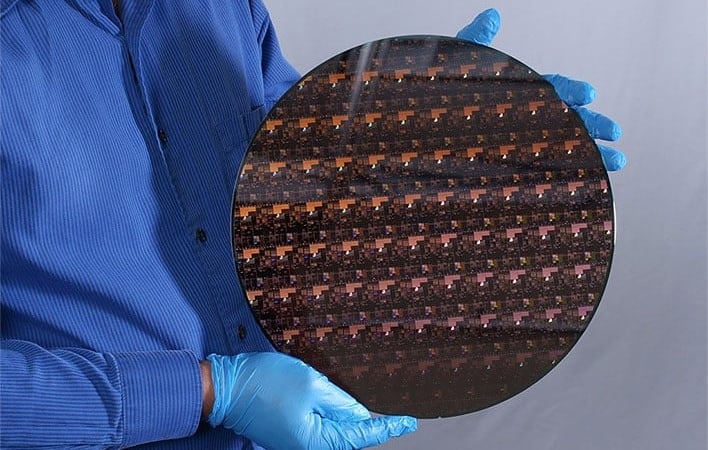

UDN Money is the source of this rumor, who also echoes earlier reports that Apple's A20 chipset will be the first major chip product to be packaged using TSMC's "Wafer-level Multi Chip Module" (WMCM) technology. This allows TSMC to integrate multiple dice at the wafer level, before dicing, which apparently allows better performance and efficiency, a reduced package size, and improved thermal behavior versus the older InFO-PoP method, largely thanks to the presence of fewer intermediary interconnects.

The majority of TSMC 2nm production isn't coming online until early next year, so we're probably at least a half year away from seeing the fruits of the chipmaker's labors. We're dying to find out if Intel's 18A is truly a worthwhile competitor for TSMC's latest and greatest, though.