JEDEC Unleashes LPDDR6 Memory To Fuel Faster Mobile And AI Devices

Power efficiency also gets a serious upgrade. LPDDR6 runs at lower voltages than LPDDR5 and introduces a new power supply scheme to help systems scale power use dynamically. For instance, during lighter workloads, devices can dial back the voltage to save battery life—something especially important in smartphones and wearables. There’s also a “dynamic efficiency mode” that lets devices shut down part of the memory system when bandwidth needs are low, trimming power use even further.

JEDEC didn’t skimp on reliability and security either. LPDDR6 adds safeguards like on-die error correction, command/address parity checking, and memory region isolation. These features work together to help prevent data corruption and detect faults early—critical in systems that can’t afford crashes or errors, like cars or medical devices. Built-in self-tests and error scrubbing functions also reduce the burden on software developers to implement their own reliability layers.

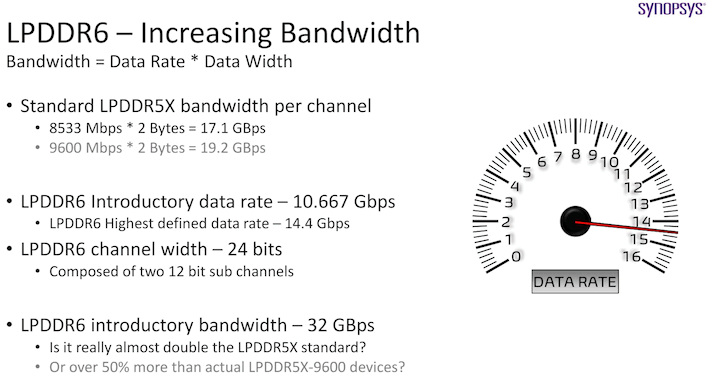

Unsurprisingly, the industry’s already lining up behind the new standard. Heavyweights like Qualcomm, Samsung, Micron, MediaTek, and SK hynix are backing LPDDR6, with many of them already building the chips, or baking support into their upcoming system-on-chip (SoC) designs. And we’re already seeing early silicon support: Cadence says it’s taped out what it claims is the industry’s first LPDDR6/5X memory IP solution, hitting speeds of up to 14.4Gbps—around 50% faster than the last-gen LPDDR5X. That could give us an idea of what to expect when the first real-world devices land with LPDDR6 under the hood.