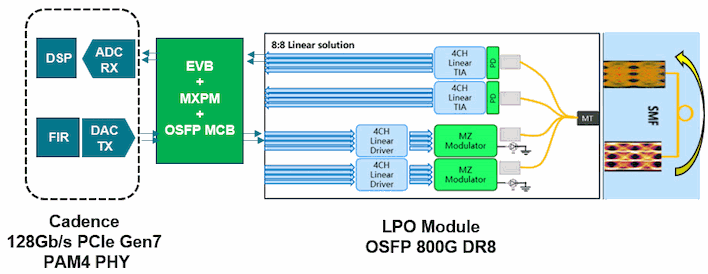

Cadence Demos Optical PCIe 7 Connection At A Blistering 128GT/s

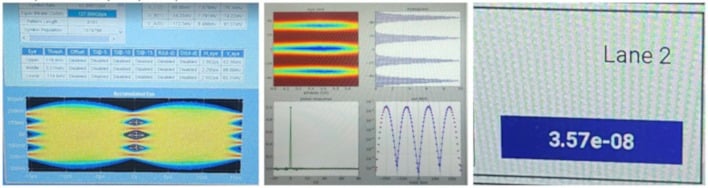

That's particularly impressive in the context that the PCIe 7.0 draft specification only mandates an error rate of no worse than 1E-6, or one error in every million bits. Cadence's IP has clearly far exceeded this requirement by a margin sufficient that commonplace Reed-Solomon Forward Error Correction (RS-FEC) can deal with the errors.

If you're thinking back to our recent coverage and thinking that 128 GT/sec sounds low, remember that we're talking about bit-level transfers on a single link. 128 GT/sec is the unidirectional transfer rate of PCIe 7.0; that gives a theoretical bandwidth of 16 GB/second, which becomes 256 GB/sec on an x16 link and thus 512 GB/second bidirectionally. As such, this is the same speed as that previous announcement.

PCI-SIG hasn't even ratified the final PCIe 7.0 specification yet; that's not expected to happen until early next year. With these early implementations, though, we could start to see devices based on PCIe 7.0 around that time, at least in the hyperscale enterprise market. Gamer plebeians like your author will have to wait a few generations before PCIe 7.0 makes its way to our systems.