Potentially Beastly Apple M1 Quadra CPU Detailed In Chip Die Map Analysis

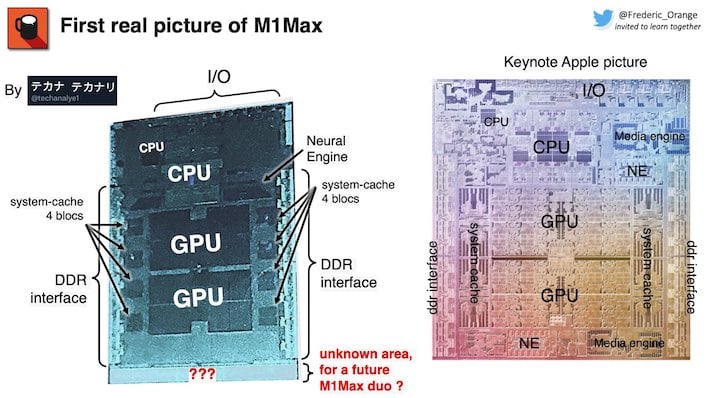

Twitter user @VadimYuryev showed the hidden section on the bottom of an M1 Max chip (seen above in our hero shot). It’s important to note, this potential interconnect was never included in Apple’s official renders of the M1 Max die.

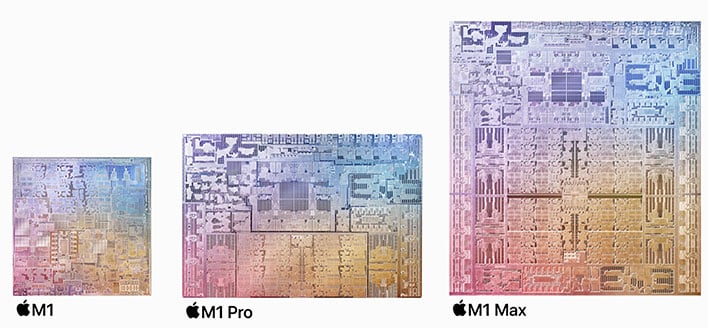

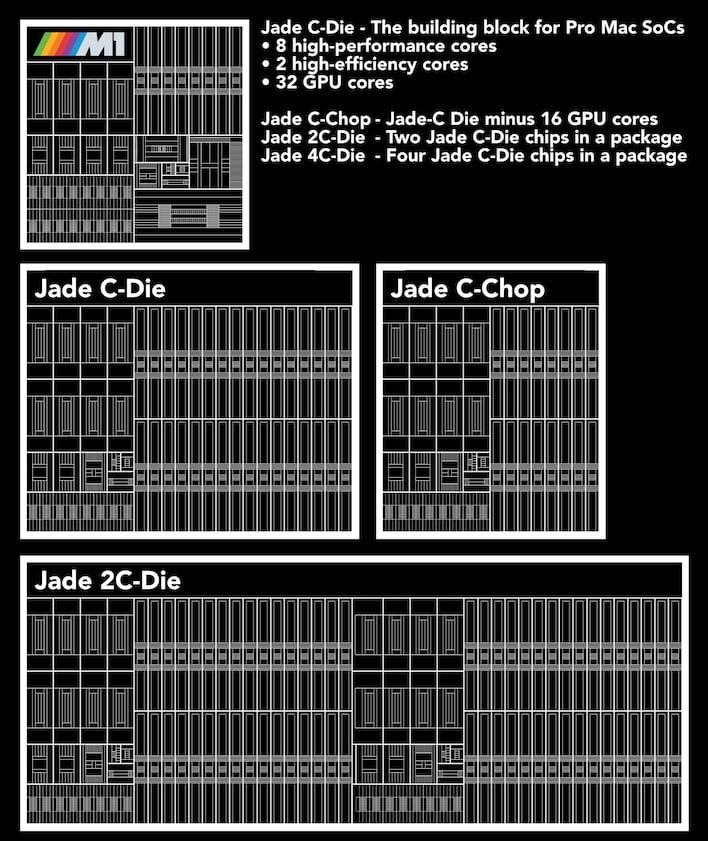

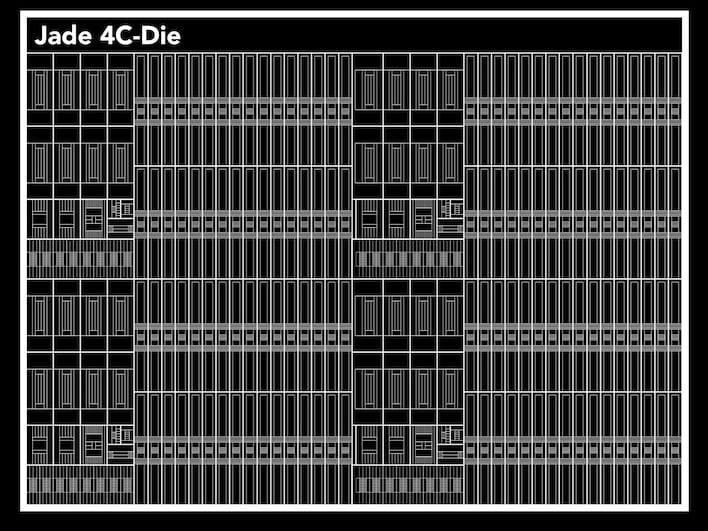

Connecting multiple M1 Max chips together in this manner would result in essentially an M1 Max Duo or even an M1 Max Quadra. Other analysts have been suggesting this possibility for months Now. In May 2021, programmer and tech writer John Siracusa suggested Jade-C as the building block for Pro Mac SoCs.

In his illustration, Siracusa shows a slimmed-down version of the M1, sacrificing 16 GPU cores for a smaller size factor. He also depicts 2C and 4C dies, joining together two and four M1 SoCs respectively into a single package.

Siracusa's illustration of the Jade-4C design concept

Apple's M1 Pro chip, an intermediate SoC between the M1 and M1 Max in terms of performance, doesn’t have the interconnect bus. This probably means Apple intends the performance scaling only for users who need it, like 3D rendering or video production workstation pros. The M1 Pro and Max already outperform most Intel processors; joining two or four of them together would definitely up the ante.