Intel Arrow Lake Doc Reveals Different Instruction Sets For Desktop And Laptop CPUs

Briefly, an instruction is essentially a way for a processor to do a specific operation (or set of operations) very quickly. Addition and multiplication are instructions, and if a CPU doesn't have a multiplication instruction, it would have to use several addition operations to effectively multiply. In the case of Arrow Lake-S and -H, the latter is missing AVX-VNNI-INT16 (an AVX instruction made for neural networks) and three encryption and decryption instructions. Realistically, that Arrow Lake-H may lack these instructions won't matter for most users, but it's an interesting potential development nonetheless.

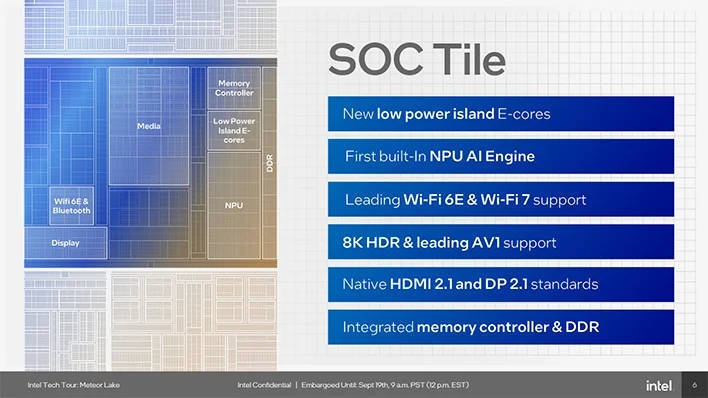

The how and why of this development the more interesting part to consider. Instructions depend on the CPU cores, and it's likely that at least one version of Arrow Lake's compute tile (the part of the chip where the CPU cores will reside) will be shared between both desktop and laptop. However, there are almost certainly two low-power E-cores in the SoC tile as well (just like in Meteor Lake), and these cores might be the reason why the desktop CPUs have more instructions.

Although the two cores in the SoC tile are largely intended for handling light duty background tasks and improving power efficiency, they are still equal to the more powerful cores on the compute tile as far as an operating system is concerned. If those two E-cores on the SoC tile don't support specific instructions, then the entire CPU can't use those instructions without a workaround. With Arrow Lake-H, it's possible that it uses the same SoC tile as Meteor Lake, which means no new instructions can be introduced despite there being a new compute tile with updated cores that may support new instructions.

Arrow Lake-S on the other hand is a desktop CPU, and with desktop CPUs battery life isn't a concern. They'll also likely have more E-cores, that are leveraged for wide variety of tasks. In that case, disabling the E-cores on the SoC tile will enable these instructions without much impact to performance. This Linux kernel commit is something of a microcosm for the potential strengths and weaknesses of Intel's new tile-based design philosphy, and how Intel can take very similar silicon and tweak it for different markets.