ARM Tapes Out Next-Gen 64-Bit Artemis Mobile Chip On 10nm TSMC FinFET Process

ARM's Artemis 10nm FinFET Test Chip

ARM has been working closely with TSMC – the Taiwanese Semiconductor Manufacturing Company – for a number of years now. Over the last six years or so especially, ARM and TSMC have collaborated to ensure that the latter’s cutting-edge process technologies work well with the former’s processor IP. So, with every generation since 2010, the companies have built ARM’s most advanced processor cores on TSMC’s most advanced emerging process nodes.

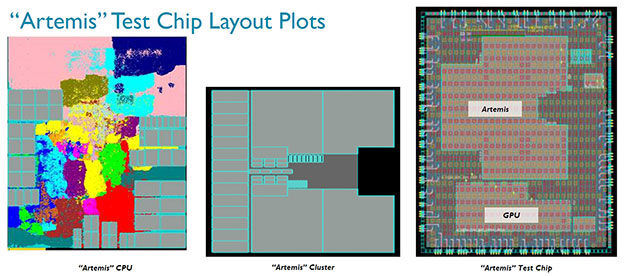

The collaboration successfully began with a test chip produced at 28nm, but today ARM is announcing the successful tape-out of a test chip featuring next-generation, premium 64-Bit ARM v8-A mobile processor cores, codenamed Artemis, and manufactured using TSMC’s upcoming 10nm FinFET process technology.

The device produced through the collaboration is a relatively simple silicon qualification test chip structure (in comparison to an actual commercial product), which gives ARM the ability to assess what the process can do with an advanced core and also provide feedback to the foundry on things like the device performance, metal stacks, and design rules. Doing this allows the company to do performance and power analysis benchmark testing and validation on 10nm FinFET silicon, before finalized designs are put into production.

The test chip features what ARM calls an Artemis cluster. It’s essentially a quad-core processor with power management IP, a single-shader Mali graphics core, AMBA AXI interconnect, and test ROMs connected to a second cluster by an asynchronous bridge that features the memory subsystem, which is stacked with a Cortex M core that handles control logic, some timers, SRAM, and external IO.

The slide above compares a fully optimized A72-based SoC produced at 16nm to an early test sample of the Artemis test chip produced with the 10nm FinFET process, and the frequencies weren’t that far off -- the delta is only around 10 - 12%. Power characteristics, however, show much improvement. Leakage was down around 10%, but dynamic power dropped by approximately 50%. ARM and TSMC expect to tweak and turn the knobs to further improve frequency scaling and performance and ultimately settle in at about a 30% power improvement, but with increased overall performance.

Click To Enlarge

Compared to 16nm FinFET+, at nominal voltage, the 10nm test chip offered a 12% performance improvement in a similar power envelope. In overdrive mode (Vod, the second annotated bullet) the test chip offered an approximate 11% performance improvement with similar power. And in super-overdrive mode (Vsod), the Artemis test chip offered similar performance, but at 30% lower power.

The 10nm FinFET Artemis test chip actually taped out all the way back in late December 2015. And ARM got working silicon back for testing and qualification a few weeks back. SoCs for premium mobile devices with next-generation cores produced on the 10nm process node are expected to arrive later in the second half of this year.

The collaboration successfully began with a test chip produced at 28nm, but today ARM is announcing the successful tape-out of a test chip featuring next-generation, premium 64-Bit ARM v8-A mobile processor cores, codenamed Artemis, and manufactured using TSMC’s upcoming 10nm FinFET process technology.

The device produced through the collaboration is a relatively simple silicon qualification test chip structure (in comparison to an actual commercial product), which gives ARM the ability to assess what the process can do with an advanced core and also provide feedback to the foundry on things like the device performance, metal stacks, and design rules. Doing this allows the company to do performance and power analysis benchmark testing and validation on 10nm FinFET silicon, before finalized designs are put into production.

The test chip features what ARM calls an Artemis cluster. It’s essentially a quad-core processor with power management IP, a single-shader Mali graphics core, AMBA AXI interconnect, and test ROMs connected to a second cluster by an asynchronous bridge that features the memory subsystem, which is stacked with a Cortex M core that handles control logic, some timers, SRAM, and external IO.

The slide above compares a fully optimized A72-based SoC produced at 16nm to an early test sample of the Artemis test chip produced with the 10nm FinFET process, and the frequencies weren’t that far off -- the delta is only around 10 - 12%. Power characteristics, however, show much improvement. Leakage was down around 10%, but dynamic power dropped by approximately 50%. ARM and TSMC expect to tweak and turn the knobs to further improve frequency scaling and performance and ultimately settle in at about a 30% power improvement, but with increased overall performance.

Click To Enlarge

Compared to 16nm FinFET+, at nominal voltage, the 10nm test chip offered a 12% performance improvement in a similar power envelope. In overdrive mode (Vod, the second annotated bullet) the test chip offered an approximate 11% performance improvement with similar power. And in super-overdrive mode (Vsod), the Artemis test chip offered similar performance, but at 30% lower power.

The 10nm FinFET Artemis test chip actually taped out all the way back in late December 2015. And ARM got working silicon back for testing and qualification a few weeks back. SoCs for premium mobile devices with next-generation cores produced on the 10nm process node are expected to arrive later in the second half of this year.