AMD Athlon 64 FX-60 - Finally, An Enthusiast's Dual Core

Core Details And Vital Signs

Same socket 939 micro-PGA package, only with two 2.6GHz Athlon 64s under the hood....

|

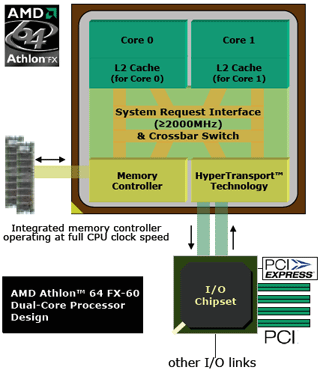

Below is a block diagram of the Athlon 64 FX-60 dual core processor. We've covered the technology and system architecture in some detail, in previous articles, so we won't re-hash much here. However, we did want to highlight a couple of key architectural differences between AMD's dual core architecture and Intel's.

Integrated Memory Controller and HyperTransport Links:

AMD's integrated memory controller on the Athlon 64 has afforded the architecture a considerable latency advantage for many generations of the processor. Conversely, this is a functional block that Intel breaks out into the Northbridge of their core logic chipsets. This does afford Intel the flexibility of being able to migrate to next generation System Memory technologies more easily but at again, at the cost of latency. In addition, AMD's bi-directional serial HyperTransport link that interfaces the CPU to the system core logic chipset, PCI Express ports and I/O expansion, is also a higher speed lower latency dedicated point-to-point architecture, versus Intel's QDR bus architecture, that is shared by Memory, PCI Express and I/O resource calls. Frankly, it's somewhat surprising to us that Intel hasn't made the move to serial interfaces on their core CPU architecture, as the benefits of latency and pin-count reduction are obvious.

System Request Interface and Crossbar Switch:

Finally, the Athlon 64 FX-60 employs the same System Request Interface (or queue manager if you will) and Crossbar Switch architecture as the Athlon 64 X2 series of dual-core chips, allowing more efficient core-to-core communication, than the current Intel dual-core architecture, which require the cores to message each other over the front side bus. There are inherent latency trade-offs within a Crossbar Switch architecture as well but without question this is a more elegant and forward looking solution than a shared bus architecture, no matter how you slice it. With the Athlon 64 X2 and Athlon 64 FX-60 core-to-core communications reside on chip.

|

Above are a few screen captures from Windows Task Manager's "Performance" tab which shows our Athlon 64 FX-60 at 50% CPU utilization driven by running one instance of Prime 95 for this simple test. Here you can see the load-balancing that is going on between the CPU cores. In addition, are screen shots from a recent version of CPU-Z which shows the Athlon 64 FX-60's dual 2.6GHz cores and their per-core dedicated 1MB of L2 cache and the 128-bit System Request Interface, which is indicated in the "bus-width" section under the cache tab.